V821 硬件设计指南

文档简介

本文档主要介绍V821芯片在IPC/门锁应用方案设计中的原理图和PCB设计要点以及细则,旨在指导客户设计,提高产品设计的可靠性以及降低产品的设计成本,保证设计质量,帮助客户缩短产品量产周期。同时请使用全志科技发布的核心模块的模板,保证产品的性能和可靠性。

原理图设计

方案概述

V821芯片介绍

V821是一颗面向智能视觉领域推出的新一代高性能、低功耗的处理器SoC,可广泛用于电池门铃、智能门锁、智能考勤门禁、网络摄像头等智能化升级相关行业。

- V821集成RSIC-V大核CPU0 @1.2GHz&小核CPU1@600MHz。

- V821内置16-bit DDR2 最高速率533MHz(528M@24MHz晶体,520M@40MHz晶体),能够满足多种应用算力及带宽需求。

- 内置全志最新一代 Smart 视频引擎,最大支持2M@25fps H.265编码和2M@60fps JPEG编解码,采用全新一代高性能 ISP 图像处理器,在2D降噪、3D降噪、HDR、边缘增强等各方面达到业内主流水平,可为客户提供专业级图像质量。

- 支持DVP以及2-lane MIPI CSI(可拆分为2套1lane)丰富的视频输入接口,最大可支持3路(2*1LAN+DVP)摄像输入。

- 支持 8bit Serial RGB & 8bit MCU & DBI 输出接口,满足各类AI视觉产品显示需求;

- 集成 IR-CUT 以及丰富的外设接口 3xTWI/4xUART/SDIO2.0/3xSPI/3xGPADC/USB2.0/I2S/DMIC 等,极大地提高了产品扩展能力。

- 全志配套提供稳定、易用的 Linux SDK 和软硬件参考设计,简化系统方案设计,降低BOM成本,能够支撑客户如IPC/门锁等产品快速量产。

V821方案介绍

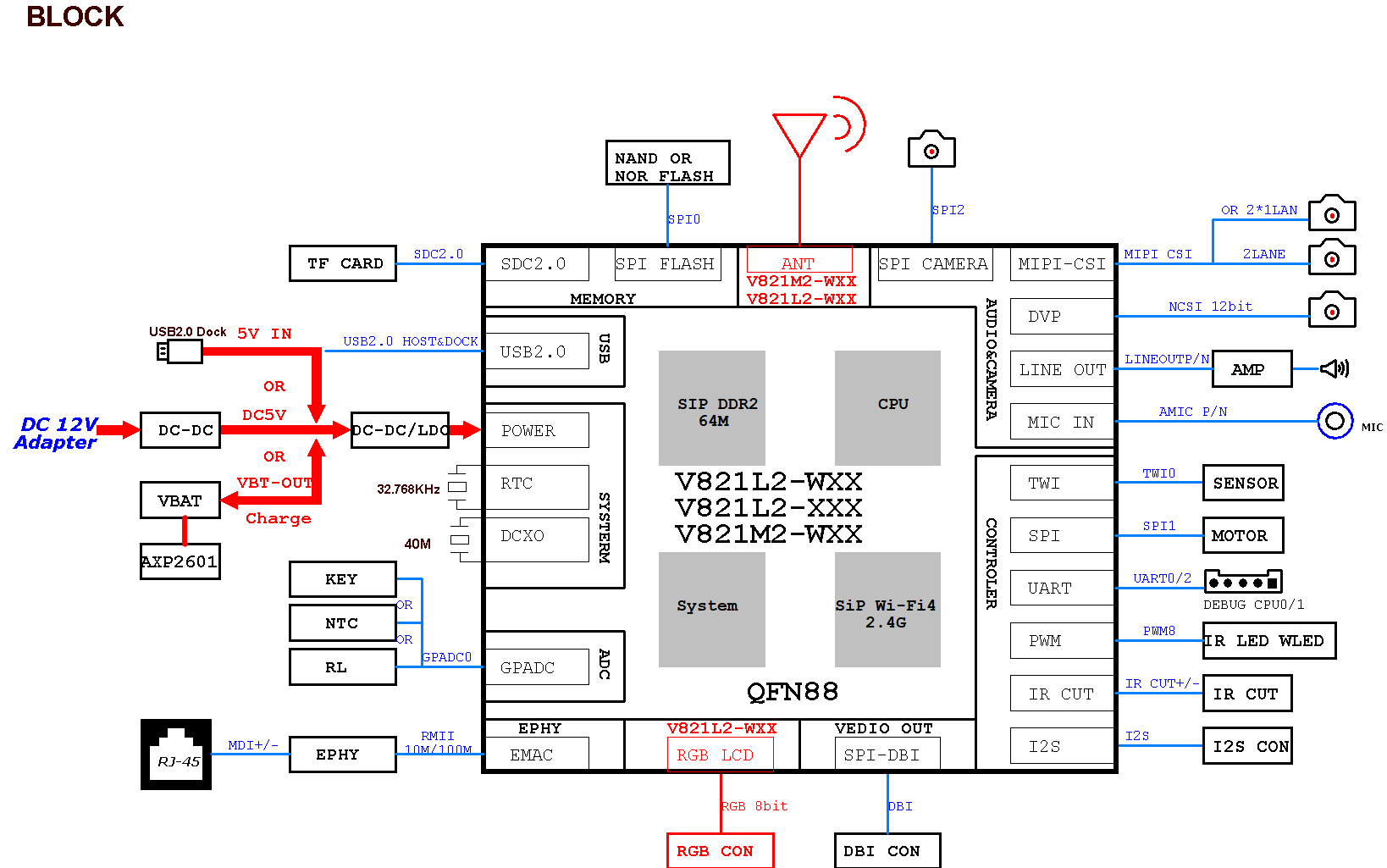

V821芯片方案系统框图,如图所示

IPC/门锁方案主要包括主芯片电路,摄像头电路、显示电路、Wi-Fi电路、音频电路、存储电路以及电源系统。V821硬件系统组成说明如下表所示:

| 系统 | 说明 |

|---|---|

| CPU小系统 | 时钟,复位,中断等 |

| 存储系统 | DRAM,EMMC,SD Card,SPI_NOR/SPI_NAND |

| 视频系统 | RGB、MIPI CSI、DVP、SPI CAMERA |

| 音频系统 | MIC IN、 LINEOUT、I2S |

| 输入输出子系统 | SPI、TWI、UART、PWM、GPADC等 |

| 电源系统 | AXP2601+DCDC/LDO |

| 无线 | 内置Wi-Fi/外挂SDIO Wi-Fi+BT |

| 电池方案PMC | PWR-EN0、PWR-EN1、PWR-EN2 |

| 其他 | 按键、G-sensor、PIR、IR-CUT、摄像头、触摸屏等 |

小系统设计电路

V821 CPU小系统包括时钟系统,系统配置PIN和DEBUG部分组成。

时钟系统信号PIN说明

V821 硬件系统包含DCXO/32K 两个时钟,对应时钟信号和对应电源说明如下表所示。

| 信号名 | 信号描述 | 应用说明 |

|---|---|---|

| DXIN | DCXO晶振输入 | DCXO晶振电路 推荐搭配40MHz晶体,保证RF性能最优。 另外可选配24MHz晶体 |

| DXOUT | DCXO晶振输出 | DCXO晶振电路 |

| X32KIN | 32K晶振输入 | 32.768K晶振电路 |

| X32KOUT | 32K晶振输出 | 32.768K晶振电路 |

| VCC18-LDO | 内部LDOA-1.8V输出 | 内部LDOA输出1.8V,可给SoC/外设1.8V供电,电流建议小于200mA |

| VCC28-LDO | 内部LDOB-2.8V输出 | 内部LDOB输出2.8V,可给sensor 2.8V供电,电流建议小于100mA |

小系统配置PIN说明

| 信号名 | 信号说明 | 应用说明 |

|---|---|---|

| PC8(BOOT-SEL0) | 启动介质配置(内部默认上拉,上拉电阻为15K) | BOOT_SEL[1:0]: 00: SPI0_NAND > NOR_Quad_SPI(PC6—PC11) > NOR_Dual_SPI(PC8—PC11) > NOR_Standard_SPI(PC8—PC11) > SDC1(PD1—PD6) > USB 01: NOR_Quad_SPI(PC6—PC11) > NOR_Dual_SPI(PC8—PC11) > NOR_Standard_SPI(PC8—PC11) > SPI0_NAND > SDC1(PD1—PD6) > USB 10: SDC0(PC0—PC5) > SPI0_NAND(PC0—PC5) > NOR_Quad_SPI (PC6—PC11)> NOR_Dual_SPI(PC8—PC11) > NOR_Standard_SPI(PC8—PC11) > SDC1(PD1—PD6) > USB 11(默认): SDC0(PC0—PC5) >NOR_Quad_SPI(PC6—PC11) > NOR_Dual_SPI(PC8—PC11) > NOR_Standard_SPI(PC8—PC11) > SPI0_NAND > SDC0(PC6—PC11) > SDC1(PD1—PD6) > USB |

| PC11(BOOT-SEL1) | 启动介质配置(内部默认上拉,上拉电阻为15K) | |

| JTAG-SEL | JTAG 配置 | 1: 软件可选择JTAG功能从PC(Default)或PD口出 0: 强制JTAG功能从PC口出 |

| FEL | 烧写程序升级PIN | 上电低电平进入烧写模式,开发量产烧写时用到 |

| TEST | IC 测试模式PIN | 浮空 |

| PMC | PMC_EN0 | 时序控制信号 |

| PMC_EN1 | 时序控制信号(电池版本) | |

| PMC_EN2 | 时序控制信号(电池版本) |

- 用户需要根据启动介质类型正确配置启动方式,BOOT-SEL PIN IO初始为内部PULL-UP上拉,通过外接4.7K电阻到地为低电平。

- TEST,实际应用浮空处理,禁止引出一段浮空走线。

- FEL/GPADC模块信号接按键时要接1nF去抖动电容,请勿删除或者更改为其他容值。

- LDOA 输出1.8V,可以给SoC 1.8V 供电,也可给外设供电,供电能力限制在200mA以内,若有任何疑问请联系全志FAE。

- LDOB 输出2.8V,可以给SoC 2.8V 供电,也可给外设供电,供电能力限制在100mA以内,若有任何疑问请联系全志FAE。

时钟电路

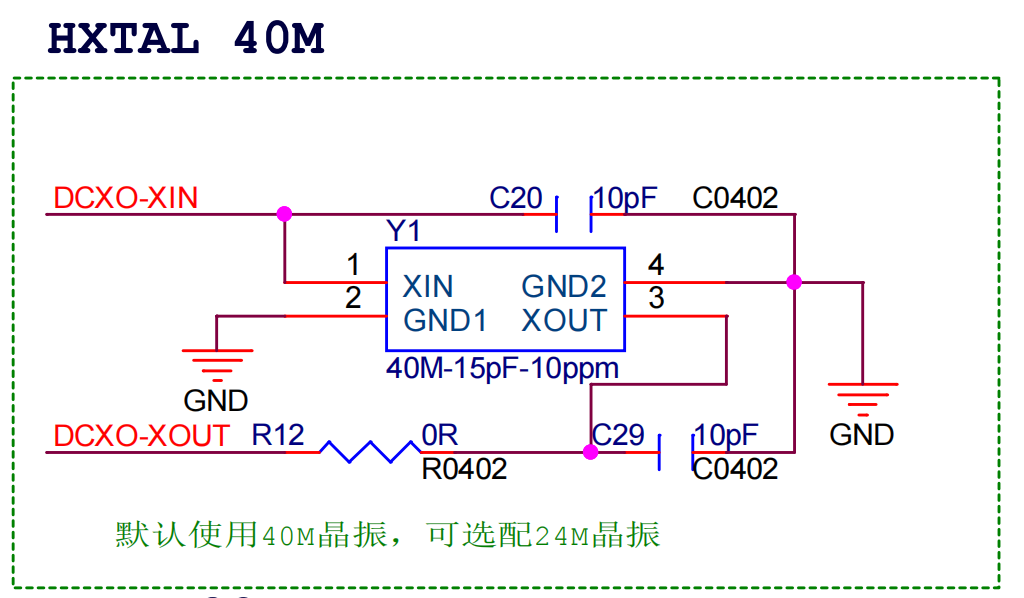

主时钟电路

V821M2-WXX/L2-WXX芯片由于内置Wi-Fi,所以默认使用40M晶振,保证RF性能最优。另外可选配24M晶振。

- DCXO模块的使用方案必须参照标案原理图进行设计。

- 外挂匹配电容大小根据晶振规格和PCB而定,要求匹配电容+SoC PIN电容+板级杂散电容总值等于晶振规格要求的负载电容大小,目前推荐晶振负载电容15PF,匹配电容10PF。

- 串接0R电阻需要预留,可能会用于后期调试振荡幅度(默认不需要调)。

- 系统时钟还可以直接由外部的晶振电路产生时钟,通过XOUT脚输入(仅作为调试用)。

晶振参数不得随意更改,需保证晶体自身负载电容、外挂匹配电容、PCB走线负载电容三者匹配。

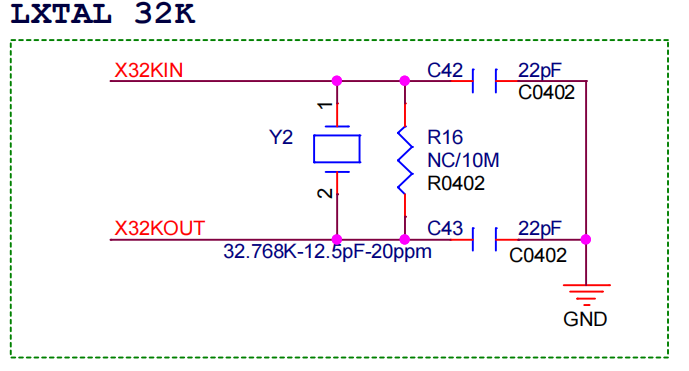

RTC时钟电路

芯片内置RTC模块,对RTC时间精度要求高场景需要外挂32.768K晶振振荡器与内部反馈电路组成时钟发生电路。设计建议如下:

- SoC内置的RTC模块带有校准功能,为确保每天时钟误差不超过一秒,建议使用32.768KHZ±20PPM晶振。

- 外挂匹配电容大小根据晶振规格和PCB而定,要求匹配电容+板级杂散电容总值等于晶振规格要求的负载电容大小,目前推荐晶振负载电容为12.5pF,外挂匹配电容为18pF,防止低温不起振。

- X32KIN/X32KOUT之间并接的预留电阻,必须保留,用于对频率微调。

- 晶振参数不得随意更改,需保证晶体自身负载电容、外挂匹配电容、PCB走线负载电容三者匹配。

- RTC时在固定分频模式,计时精度主要取决于外置晶体,请综合考虑晶体频率误差、温度漂移等因素,选择合适的晶体;

- 对计时精度要求较严格的产品,建议选择外置高精度集成RTC。

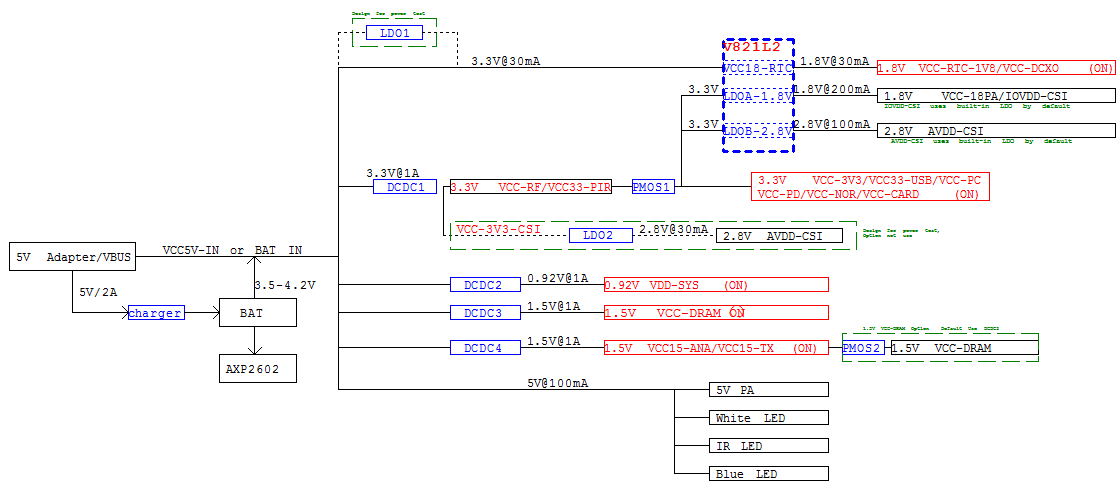

电源系统设计

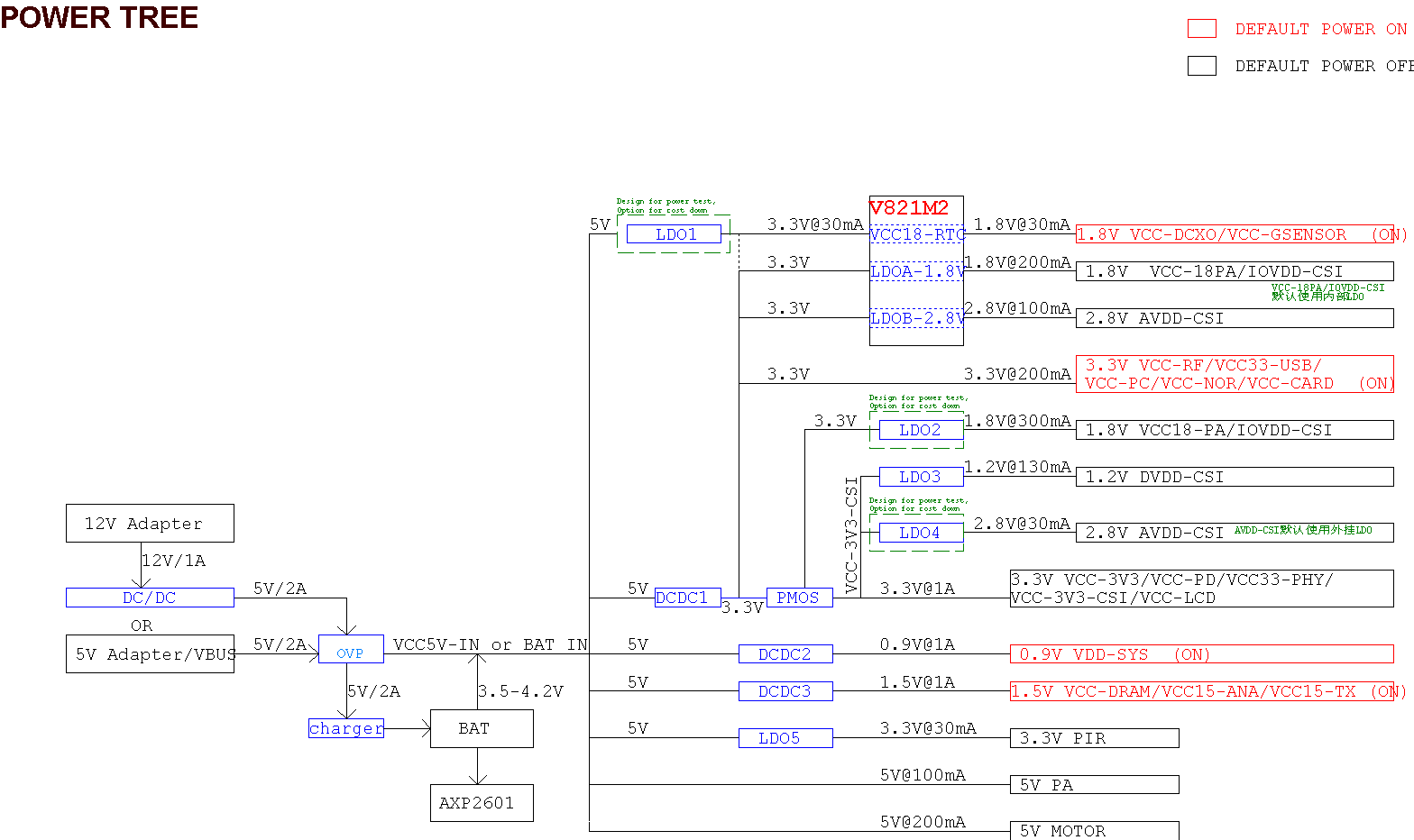

V821 电源系统架构介绍

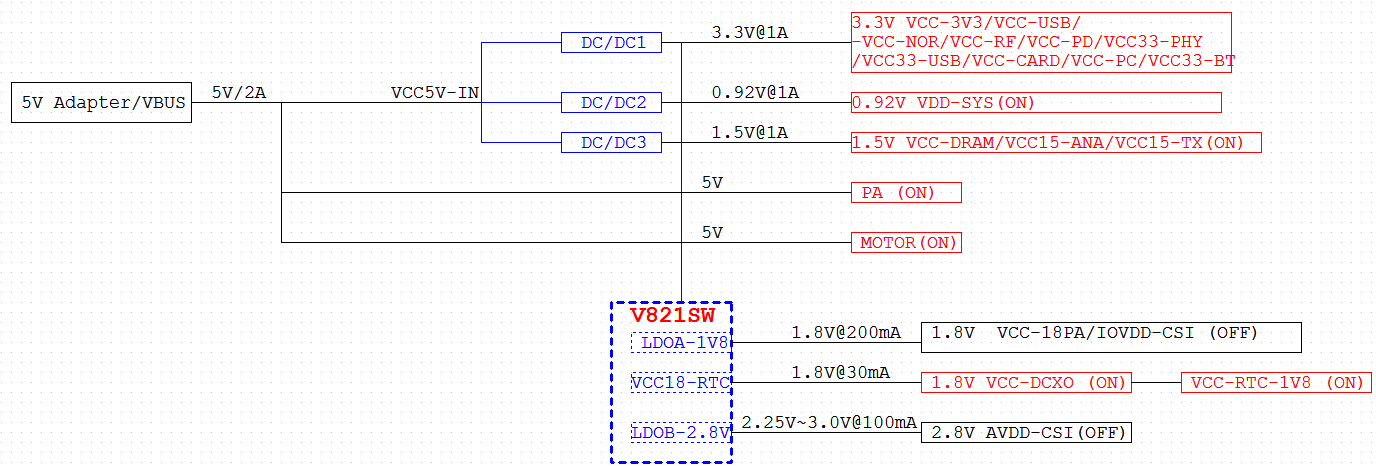

V821电源供电系统主要由DCDC/LDO组成。

V821方案电源设计说明如下:

- 为确保V821部分模块在BOOT阶段要求上电的需求,请不要改变各路电源所使用的LDO和DCDC。

- 电源POWER TREE 设计按照标案默认分配进行设计,避免因电源改动增加产品部分场景功耗,同时也增加软件适配工作量。

- 对于合并在一起供电的部分SoC 模块电源,已经经过系统验证测试,不能随意更换搭配,避免导致系统不稳定,如VCC-3V3 等。

- DCDC1/DCDC2/DCDC3电感参考值为:感量为2.2uH,要求此路最大电流不超过电感饱和电流的80%,直流电阻小于100毫欧。

- DCDC3(VCC-DRAM) 给DDR供电,初始上电值为1.5V,由硬件根据调节反馈电阻值输出1.5V/1.8V。

- VBAT可直接给VBAT_RTC供电,参考设计只是预留LDO1给VBAT_RTC 供电,默认为常供电状态。

- V821系统复位信号AP-RESET由内部复位产生。

- VCC-PL有1.8V 和3.3V 两种电压,PL0、PL1固定电平1.8V,P2-PL7默认电平3.3V,可配置为1.8V。

- V821自带一LDOA-1.8V(3.3V转1.8V),LDOA可以给系统1.8V 供电,但不建议超过200mA,设计时请预留外挂LDO2-1.8V,根据产品实测发热情况确定是否使用LDOA。

- V821自带一LDOB-2.8V(3.3V转2.8V),LDOB主要给摄像头SENSOR 2.8V 供电,但不建议超过100mA,设计时请预留外挂LDO4-2.8V,根据产品实测发热情况确定是否使用LDOB。

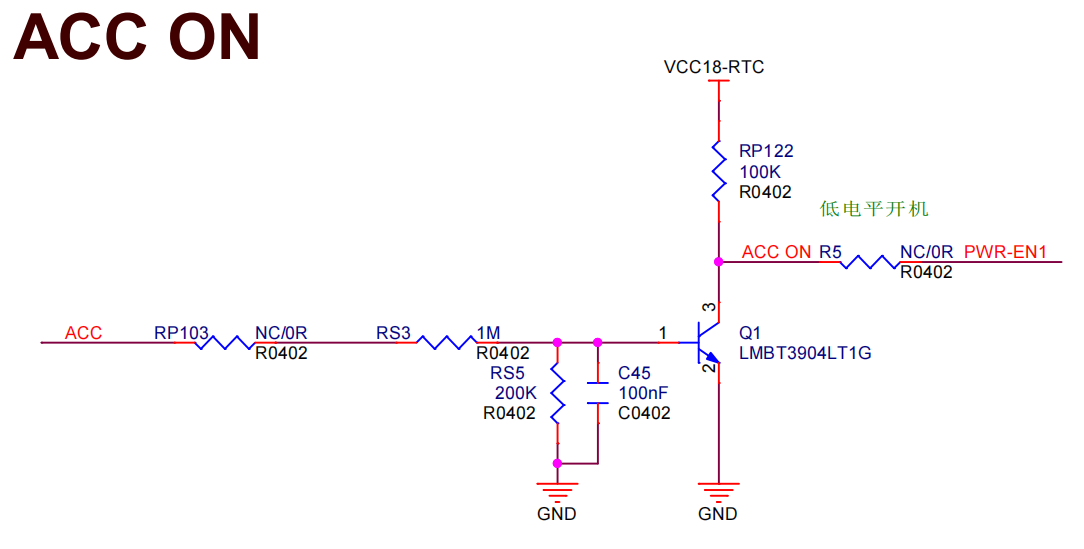

- VCC18-RTC 是常供电源,供电能力约30mA,一般是给 VCC18-DCXO 时钟系统供电,同时提供休眠唤醒状态下提供检测电平,例如 ACC 检测,开机按键。

V821 PL 口 IO

V821系列各型号的的 RTC 域 PL 口应说明如下:

-

只有RTC域的PL口IO具备唤醒/开机的功能。

-

PL6 在VBAT-RTC上电后第一次启动不可为高电平,之后只要VCC-RTC不掉电则没有限制要求

-

V821M2-WXX/WBX(芯片不具备唤醒/开机功能)、

- Power Cntrol IO:PL0;

- PL0~1固定为1.8V IO;

- PL2~PL7启动默认为3.3V IO

-

V821L2-XXX/BXX/WXX/WBX&V821DB-WBX(芯片具备唤醒/开机功能),唤醒外设的唤醒中断电平只能为1.8V

- Power Cntrol IO:PL0~PL1;

- PL0~1固定为1.8V IO;

- V821L2-XXX/BXX:

- PL2~PL7启动默认为3.3V IO;

- V821L2-WXX/WBX&V821DB-WBX

- PL2~PL7启动默认为1.8V IO。

-

V521D2-WXX(具备唤醒/开机功能),唤醒外设提供的唤醒中断电平只能为1.8V

- Power Cntrol IO:PL0;

- PL0~1固定为1.8V IO;

- PL2~PL7启动默认为1.8V IO。

-

所有型号在启动后可软件自由切换PL2~PL7的电源域(1.8V/3.3V)(注:整组切换,不支持单个IO切换)。

-

若因设计原因未使用,或只使用了其中一个IO,剩余的Power Cntrol IO不可作为其他功能使用,需要保持NC。

V821 上下电时序介绍

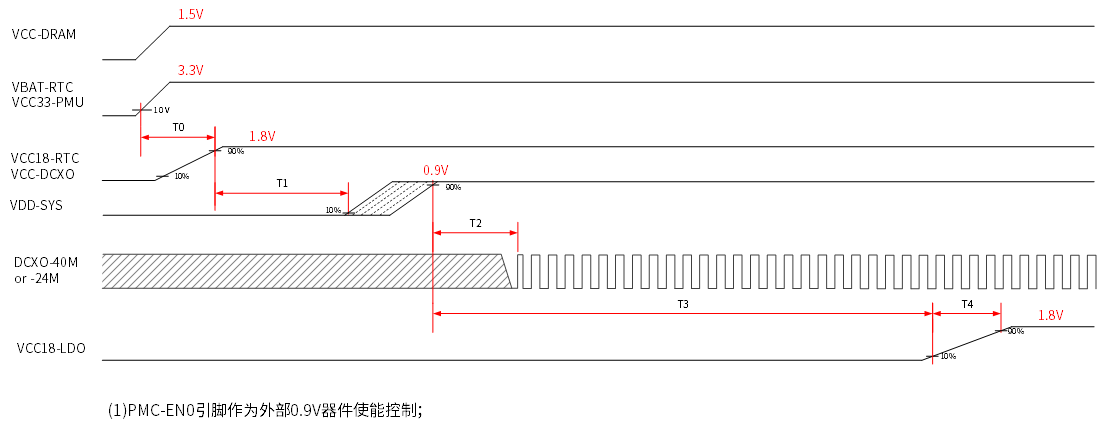

V821 (SoC带PMC)上电时序描述如下:

- VCC-DRAM,VBAT_RTC,VCC33-PMU&VCC33-PC可一上电;

- 其他电源需等到VDD_SYS稳定之后上电,VCC18_RTC不晚于VCC_DRAM上电;

各路电源上电步骤如表所示。

| 电源 | 电压 | 上电步骤 |

|---|---|---|

| VCC_DRAM | 1.5V/1.8V | 1 |

| VBAT_RTC | 2.1V~6.0V | 1 |

| VCC33-PMU&VCC33-PC | 3.3V | 1 |

| VCC18-RTC,VCC-DCXO | 1.8V | 2 |

| VDD-SYS | 0.9V | 3 |

| 40M or 24M CLK | - | 4 |

| VCC18-LDO | 1.8V | 5 |

V821上电时序要求如下图所示。

| Parameters | Description | Min | Typ | Max | Unit |

|---|---|---|---|---|---|

| T0 | 从 VBAT-RTC/VCC33-PMU 开始上升到 VCC18-RTC/VCC-DCXO 稳定的延迟时间 | 80 | - | - | us |

| T1 | 从 VCC18-RTC/VCC-DCXO 稳定到 PMC-EN0 启用的延迟时间 | 1.1 | - | 3.5 | ms |

| T2 | 从 VDD-SYS 稳定到 DCXO 稳定的延迟时间 | 0 | - | - | ms |

| T3 | 从 VDD-SYS 稳定到 VCC18-LDO 开始上升的延迟时间(40M晶振)(不带BLE系列) | 24.0 | - | 35.0 | ms |

| 从 VDD-SYS 稳定到 VCC18-LDO 开始上升的延迟时间(40M晶振)(带BLE系列) | 8.0 | 16.0 | |||

| T4 | VCC18-LDO 稳定时间 | 50 | - | 150 | us |

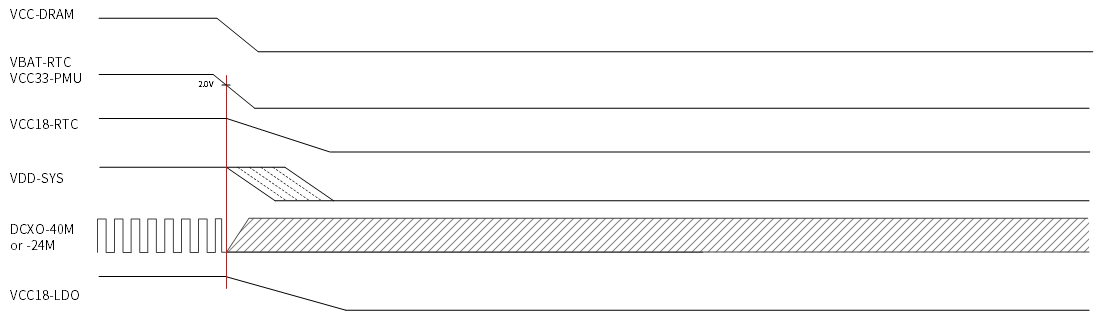

V821下电时序描述如下:

- SoC接收到下电指令后,SoC拉低内部Reset信号,其他电源域同时下电,每路电的下降时间由电源的负载决定。

V821 下电时序要求如下图所示

SoC端电源质量要求

V821 SoC 端电源精度和纹波噪声要求如下表所示。

| 序号 | 电源名称 | 电压精度 | 纹波要求 | 噪声要求 |

|---|---|---|---|---|

| 1 | AVCC | 1.8V± 2% | <1.5% | <2.5% |

| 3 | VCC33-USB | 3.3V± 10% | <5% | <10% |

| 4 | VCC18-MCSI/VCC18-PA | 1.8V± 5% | <1.5% | <2.5% |

| 5 | VBAT-RTC | 3.3~4.2V | <5% | <10% |

| 6 | VCC33-RF | 3.3V± 10% | <5% | <10% |

| 7 | VCC15-ANA | 1.5V± 5%1.8V± 5% | <5% | <10% |

| 8 | VCC15-TX | 1.5V± 5%1.8V± 5% | <5% | <10% |

| 9 | VCC33-PC/VCC33-PD | 3.3V± 10% | <5% | <10% |

| 10 | VDD-SYS | 0.9~1V | <80mV | <80mV |

| 11 | VCC-DRAM | 1.5V± 5%1.8V± 5% | <100mV | <100mV |

V821 SoC 电源电容设计

V821 SoC 端各电源建议容值如下:

- 系统SYS包含了ISP/VE模块,采用独立电源域供电,一般不进行调压(休眠下可调压),VDD-SYS至少要有一个10uF以上的电容靠近SoC正下方放置,VDD-SYS纹波噪声严格控制在80mV以内,并保证电压不低于频率要求的最低电压值,具体参照《CPU频率电压对应表》。

- VBAT-RTC电源外挂100nF电容,VCC18-RTC(内部LDO转化而来给晶振供电的电源)电源外挂1uF电容,靠引脚放置;

- VCC18-MCS&VCC-PA电源外挂100nF电容,靠引脚放置;VCC33-PC/VCC33-PD电源外挂10uF电容,靠引脚放置;VCC33-USB等GPIO电源外挂100nF电容,靠引脚放置;

- VCC-RF电源外挂100nF电容,VCC15-ANA/VCC15-TX电源外挂1uF电容,靠引脚放置;

- AVCC等电容参照音频电路设计章节。

- LDOA 电源输出需要外挂2.2uF电容,靠引脚放置,若实际方案中未使用此LDOA,则电容可NC。

- LDOB 电源输出需要外挂10uF、2.2uF和100nF电容,靠引脚放置,若实际方案中未使用此LDOB,则电容可NC。

SYS电源推荐电容组合如图所示。

数字低压供电VDD-SYS、VCC-DRAM等电源涉及到系统稳定和可靠性,电源电容必须按照标案原理图和PCB设计。设计完成时需重点检查这几个数字模块PCB走线以及电容摆放位置,产品测试时检查这几路供电电源纹波是否满足纹波要求。

PMC 相关设计

一般来说,PMC IO 控制的对应关系对应下表所示:

| 方案 | PMC_EN0/PL0 | PMC_EN1/PL1 | PMC_EN2/PL2 | PL6 | 休眠唤醒支持的模式 |

|---|---|---|---|---|---|

| 常电/CDR方案 | PMC | GPIO | GPIO | GPIO | 支持 poweroff 关机模式 |

| 电池方案,不使用调压功能 | PMC | PMC | GPIO | GPIO | 支持 super standby, ultra standby, poweroff 模式 |

| 电池方案,使用调压功能 | PMC | PMC | PMC | GPIO | 支持 super standby, ultra standby, poweroff 模式,支持动态调压 |

| 电池方案,不使用调压功能,AOV | PMC | PMC | GPIO | PMC | 支持 super standby, ultra standby, poweroff 模式,支持独立控制 DRAM 电源 |

| 电池方案,使用调压功能,AOV | PMC | PMC | PMC | PMC | 支持 super standby, ultra standby, poweroff 模式,支持独立控制 DRAM 电源,支持动态调压 |

PMC_EN0/PL0 默认作为 PMC 功能,这个引脚在硬件设计时请尽量不用做普通 IO

常电 IPC 方案

- VDD-SYS晚于3.3V上电

- PMC_EN0/PL0:控制 VDD-SYS上电时序,建议不作为 GPIO 使用(限制较多)

- PL1~PL7 用户可作为 GPIO 使用

CDR 方案

- PMC_EN0/PL0:控制 VDD-SYS上电时序

- PL1~PL7 具备唤醒/开机功能(唤醒电平只能为1.8V)

- 唤醒源可支持做ACC DET,G-INT,VBUS-DET,PWRON(需接到PL口IO上)

- 一路12V转5V DCDC+SOC三路DCDC供电(3.3V,0.92/1V,1.5V)+一路G-SENSOR LDO供电。若AHD/CMOS需1.2V则需增加一路LDO/DCDC供电

- VBAT-RTC可直接电池或者纽扣电池供电,无需外挂LDO(电池需外挂charger芯片)

- SOC 电源输入采用 MOS 管开关方式控制,关机下可断开 DCDC 输入源,避免 DCDC 漏电影响功耗

- 关机下保持VBAT-RTC供电以及外设G-SENSOR供电其他均断电

- VBUS-DET 和 ACC 需通过隔离转换到 1.8V 接入到 PL 口 IO 实现接入唤醒/开机功能,开机后可作为普通 IO,实现 VBUS 和 ACC 状态检测

- VBAT-RTC输入电压范围 2.1~6V,单节锂电池方案,可直接接到 VBAT-RTC,实现常供 RTC 不掉电

- 纽扣电池方案,可纽扣电池直接接 VBAT-RTC,无需外挂 LDO

- 当正常关机 (hibernation),VBAT-RTC 功耗 10uA 左右,若非正常关机,异常掉电状态,VBAT-RTC 功耗 40uA 左右

- 如果对非正常关机功耗要求较高,需外挂RTC芯片降低功耗

电池IPC/门铃方案

电池IPC/门铃方案需要 4 路 DCDC,包括 3 路低静态漏电 DCDC 3.3V,0.92V/1V,1.5V + 1路普通DCDC 1.5V + 1路LDO(唤醒外设PIR等供电)+ 1路PMOS开关(3.3V非唤醒源外设/IO供电)

- DCDC1 为 RF 3.3V 供电(需低静态漏电)

- DCDC2 为 VDD-SYS 0.92V/1V 供电(需低静态漏电)

- DCDC3 为 DRAM 1.5V 供电

- DCDC4 为 RF 1.5V 供电(需低静态漏电)

- PMOS1 为 3.3V 非唤醒源外设/IO 供电

- LDO1 为唤醒源外设供电,如 PIR,Gsensor 等

- 电池为单节电池可直接接 VBAT-RTC,确保 VBAT-RTC 不掉电,若为多节电池,需额外增加降压电路,保证输入到 VBAT-RTC 在 2.1V~6V 范围内

PWR-EN0 和 EN1为硬件控制,触发唤醒源,由硬件拉高IO,EN2(PL2)为软件控制,启动时可由软件控制拉高,不需要使用可做普通IO/唤醒IO使用:

- PWR-EN0(PL0):控DCDC1-3V3(RF3.3V),DCDC4-1V5(RF1.5V),DCDC2-0V92/1V(VDD-SYS)

- PWR-EN1(PL1):控DCDC3-1V5(VCC15-DRAM),PMOS1(非唤醒源外设和IO供电)

- PWR-EN2(PL2):做双目控制DCDC2 (VDD-SYS)在休眠下调压达到休眠降功耗的作用(若无需做调压,PL2可释放出来做普通IO使用)

工作模式与电源供电方式:

- 正常工作/唤醒状态模式:PL0,PL1,(PL2)都拉高,DCDC 均开启供电

- Wi-Fi保活模式:PL0拉高,PL1,(PL2)拉低;保持VBAT-RTC(VCC18-RTC),RF供电(3.3V和1.5V),小核供电(0.92V/1V),不掉电;其他除唤醒源外电源(PMOS+DRAM1.5V)均掉电;支持 WIFI 唤醒,IO(PL2~PL7)唤醒,RTC定时唤醒

- hibernation(关机)模式:PL0,PL1,(PL2)都拉低;只保持VBAT-RTC(VCC18-RTC)不掉电;其他电源都掉电;此模式只支持IO(PL2~PL7)唤醒,RTC定时唤醒

- 休眠保活下需常供电的 DCDC 必须选用低静态漏电的 DCDC(quiescent current 5uA)

- DCDC1-3V3 (RF3.3V) ---- 考虑 WIFI 瞬态峰值较高,以及 MOS 管开启抽电电流影响,建议选用 1A 以上的 DCDC

- DCDC4-1V5 (RF1.5V) ---- 平均电流较小,瞬态较高,要求 DCDC 选择 500mA 以上

- DCDC2-0V92/1V (VDD-SYS) ---- 电流稳定,瞬态不会太高,0.8A 以上 DCDC 可满足

- DCDC3-1V5 (VCC15-DRAM) 休眠保活下常关,无静态漏电要求,带载选择 500mA 以上

- 对于其他唤醒外设供电要求,建议选用低静态漏电的 LDO

- DCDC 的分压电阻阻值建议选用百 K 级别以上,降低外围的静态漏电流

电池 WIFI AOV 方案

主要供电路径:

- 单节电池无需要另外加 DCDC 转换,可直接到后级 DCDC 上

- 唤醒外设中断需接到PL口IO上

- 输入源做VBUS和VBAT电源输入切换选择,对二极管选型要求最大正向电压在350mV@1A以内,反向漏电要求小于5uA

- 4 路 DCDC(3路低静态漏电DCDC 3.3V,0.92V/1V,1.5V+1路普通DCDC 1.5V)+3路LDO(1路LDO供唤醒外设PIR等和2路LDO供CMOS 1.8V和2.8V,若需1.2V需再增加1路LDO)+2路PMOS开关(3.3V非唤醒源外设/IO供电和CMOS供电)

其中电源方案如下:

- DCDC1 为 RF 3.3V 供电(需低静态漏电)

- DCDC2 为 VDD-SYS 0.92V/1V 供电(需低静态漏电)

- DCDC3 为 DRAM 1.5V 供电

- DCDC4 为 RF 1.5V 供电(需低静态漏电)

- PMOS1为 3.3V 非唤醒源外设/IO供电

- PMOS2 为 CMOS 供电 LDO 的 3.3V 输入源(LDO2~LDO4输入)

- LDO1 为唤醒源外设供电,如 PIR 等

- LDO2~LDO4 为 CMOS 独立供电 LDO 1.2V,1.8V,2.8V(通用设计,这里不体现)

- 电池为单节电池可直接接 VBAT-RTC,确保 VBAT-RTC 不掉电,若为多节电池,需额外增加降压电路,保证输入到 VBAT-RTC 在 2.1~6V 范围内

需要控制外部电源的 PMC 与 IO 如下:

- 电源上通过 PL0,PL1,PL2 和 PL6 控制,其中 PL0 和 PL1 为硬件控制,触发唤醒源,由硬件拉高 IO,PL2 和 PL6 为软件控制,启动时由软件控制拉高

- PL0(PWR-EN0):控DCDC1-3V3(RF3.3V),DCDC4-1V5(RF1.5V),DCDC2-0V92/1V(VDD-SYS)

- PL1(PWR-EN1):控PMOS1(非唤醒源外设和IO供电)

- PL2(PWR-EN2):做双目控制DCDC2(VDD-SYS)在休眠下调压达到休眠降功耗的作用(若无需做调压,PL2可释放出来做普通IO使用)

- PL6:控DCDC3-1V5(VCC15-DRAM),PMOS2

各休眠状态芯片内电源输出情况

| 状态 | VCC18-RTC | LDOB-2V8 | LDOA-1V8 |

|---|---|---|---|

| 超级待机模式 Super Standby | 常供 | 可配,默认关 | 可配,默认关 |

| 超低功耗待机模式 Ultra Standby | 常供 | 可配,默认关 | 可配,默认关 |

| 关机模式 Hibernate | 常供 | 关 | 关 |

- 配置方式请参考 :[Standby - 休眠唤醒]

FLASH设计

V821 支持SPI/eMMC,当使用不同介质时,需要正确配置BOOT-SEL,具体参照系统配置章节。

SPI设计说明如下:

| 信号名 | 内置上下拉 | 应用说明 |

|---|---|---|

| SPI-MISO | NA | 直连 |

| SPI-MOSI | NA | 直连 |

| SPI-CLK | NA | 在SoC端串接33R电阻 |

| SPI-CS | 内置15K上拉 | 直连,外部预留上拉电阻到VCC33-PC,默认使用内部上拉 |

| SPI-WP | 内置15K上拉 | 直连,外部预留上拉电阻到VCC33-PC,默认使用内部上拉 |

| SPI-HOLD | 内置15K上拉 | 直连,外部预留上拉电阻到VCC33-PC,默认使用内部上拉 |

SPI参考设计见图所示。

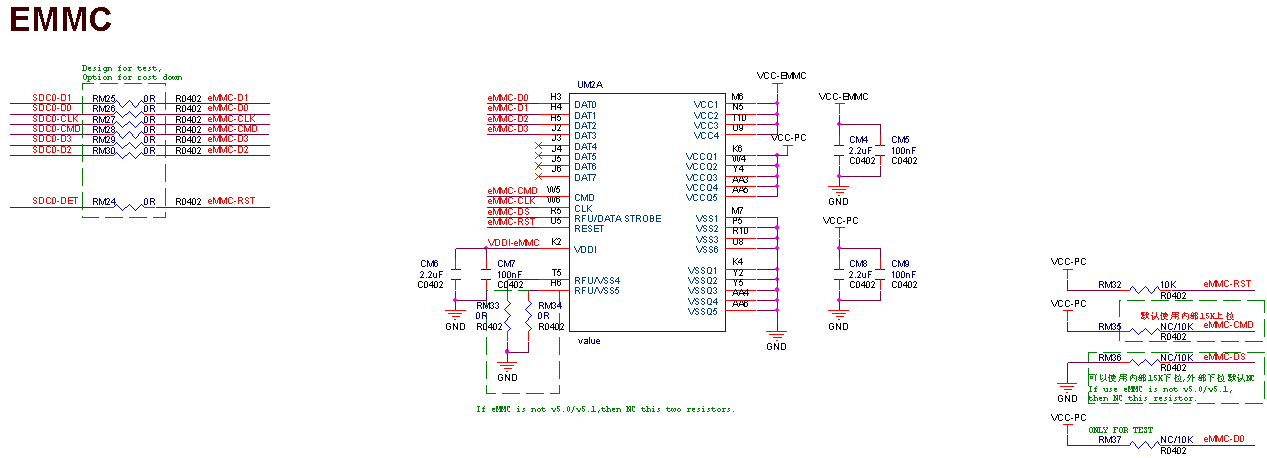

EMMC设计说明如下:

- 如果使用eMMC 5.0 及5.0以上的片子,则eMMC的PIN T5和H6需要通过0R电阻到地,V821 芯片集成了eMMC-DS 下拉电阻,eMMC-DS信号线下拉电阻可NC处理。而其他非eMMC5.0/5.1的片子,则eMMC的PIN T5和H6 R5的下拉电阻需要NC。具体可参照eMMC datasheet作处理。

EMMC 上下拉匹配设计推荐如表所示。

| 信号名 | 内置上下拉 | 应用说明 |

|---|---|---|

| eMMC-D[0:3] | NA | 直连 |

| eMMC-CLK | NA | 在SoC端串接33R电阻 |

| eMMC-CMD | 内置15K上拉 | 直连,外部预留上拉电阻到VCC33-PC,默认使用内部上拉 |

| eMMC-RST | 内置15K上拉 | 直连,外部预留上拉电阻到VCC33-PC,默认使用内部上拉 |

| eMMC-DS | 内置15K下拉 | 直连,外部预留下拉电阻到地,默认使用内部下拉 |

eMMC参考设计见图所示。

eMMC、SPI NOR、SPI NAND选型请参考客户服务平台物料库内对应推荐选型表,必须选用支持列表里V821平台支持的型号。

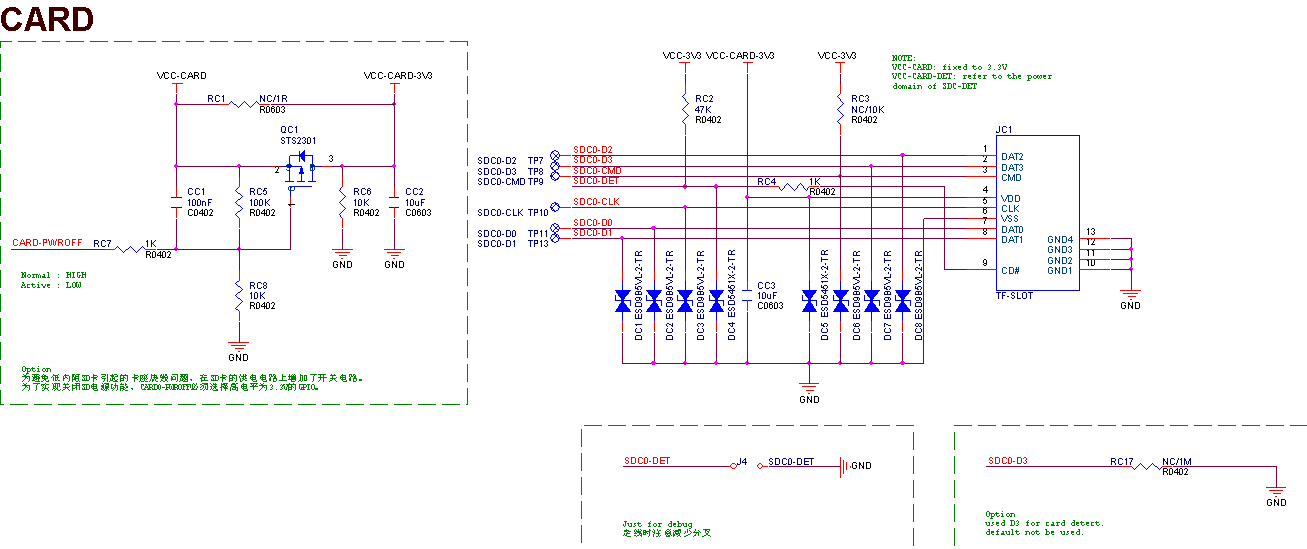

SD Card 电路设计

V821 PC 口支持 SD2.0 协议。

- 电路设计建议如下:

- CMD信号内部可以通过15K电阻上拉到PF口电压,也可使用外部上拉电阻。

- SDC0-DET卡检测信号可以使用内部15K电阻上拉,也可使用外部上拉电阻。

- 卡检测也可以用SDC0-D3的下拉1MR电阻作为卡检测。

- CLK信号串接33R电阻,若CLK上并接电容,容值不能超过5pF。

- VCC-CARD 建议使用CMOS开关控制电路,避免插入坏卡时将系统电源拉低,同时遇到静电问题时可执行Card掉电复位功能,开关电路后级建议加上对地10K泄放电阻,软件控制card掉电时需保持200mS以上。如果为了降低产品成本,建议改为串接1R~2.2R电阻。

- CMD/CLK及DATA线上并接的TVS,根据实际情况选择是否需要贴片,TVS容值不宜超过10pF。

- 卡检测SDC0-DET信号串接1K电阻,提高ESD性能。

CARD IO 供电SoC内部实现的参考设计如图所示。

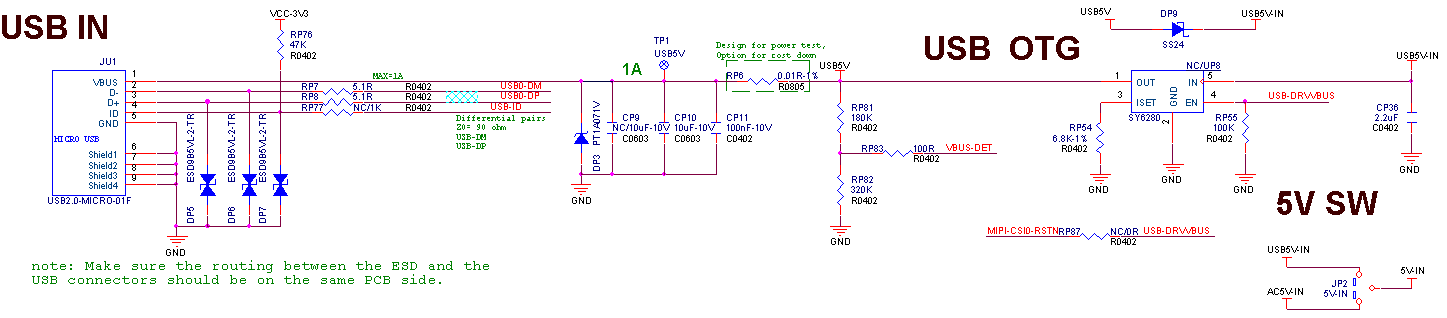

USB电路设计

V821有1套USB接口,USB0具有OTG功能,在产品功能定义上需要注意区别。

- V821 SoC USB 的USB 模块有两路供电,分别为VCC-USB 和VDD09-USB,供电说明如下:

- 超级待机需要支持USB 唤醒时,VCC33-USB和VDD-SYS 供电不能关闭,VCC33-USB采用DCDC1-3V3供电,VDD-SYS采用DCDC2-0V9供电,此时USB-5V 也不能关闭。具体参照标案设计。

- USB0座子上的ID 信号为OTG 检测信号,需要增加上拉电阻到对应IO电压。若ID检测为低,则主控识别为USB外设接入,USB0工作为Host模式。反之USB0工作在Device模式。

- ID信号到SoC端的GPIO 串接1K~1.5K电阻提升ESD性能。

- D+/D-信号线为高速信号线,并接的TVS要求低容值,否则影响数据传输,以小于4pF为宜。

- USB电源限流器件EN使能管脚加下拉电阻,默认关闭,只有作为HOST,为外部设备供电时才打开。

USB推荐电路如图所示。

显示屏电路设计

V821支持Serial RGB/I8080(仅V821L2-WXX支持RGB/I8080)、SPI屏接口,设计建议如下:

- 产品设计时请根据具体的LCD规格选用相关的参考电路设计,RGB 接口供电按照屏规格参数进行调整。

- LCD的IO电压与AP端的控制IO电压是否一致,若不一致,注意做电平匹配处理,如LCD-RST 信号。

- RGB接口的数据线和控制线上串接33R电阻,LCD-CLK串接33R电阻,靠近SoC摆放,并且预留对地电容,靠近接口摆放,减少信号反射,方便解决EMI问题。

- RGB接口LCD-RST信号建议预留对1nf电容,靠近接口摆放。

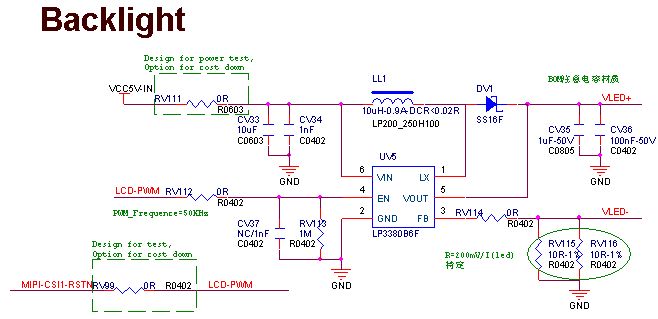

- LED背光电路中肖特基二极管建议选择反向击穿电压比背光IC OVP电压大的,这样可以避免出现在未接屏负载下烧坏二极管的现象。

- LED背光电路中输出电容的耐压值要大于背光IC OVP电压,推荐选用耐压值为50V的滤波电容。

- 推荐使用一个LCD-PWM信号接背光IC(EN管脚支持PWM调节)实现背光亮度调节和开关屏。PWM频率建议20Khz以上推荐50Khz(避开音频频率),LED背光IC的EN脚,需要加下拉电阻,防止上电过程中IO有毛刺出现屏闪现象。

- 背光IC 的FB 端对地的限流电阻选用1%精度的电阻,封装的选用需满足电路的功率需求。

RGB背光电路参考设计如图所示。

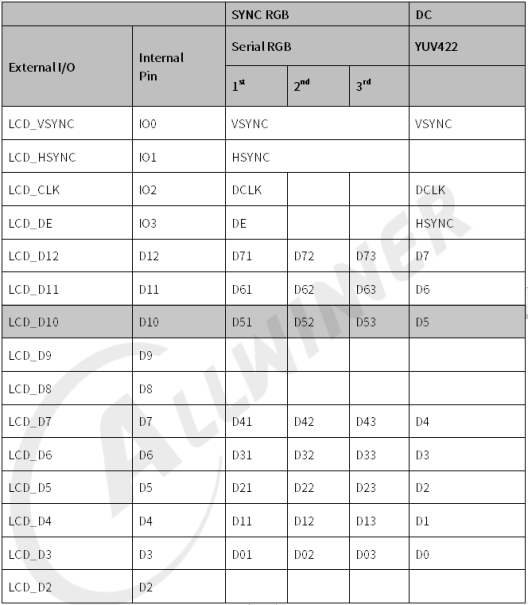

RGB Serial RGB/CPU屏各种类型接口 mapping 关系如图所示。

8/9/16 bit CPU屏接法说明如表所示。

| SoC PIN | SRGB | 16bit-CPU(不带TE) | 9bit-CPU(不带TE) | 8bit-CPU(不带TE) | 16bit-CPU(带TE) | 9bit-CPU(带TE) | 8bit-CPU(带TE) |

|---|---|---|---|---|---|---|---|

| LCD-VSYNC | LCD-VSYNC | LCD-CS | LCD-CS | LCD-CS | TE | TE | TE |

| LCD-HSYNC | LCD-HSYNC | LCD-RD | LCD-RD | LCD-RD | LCD-RD | LCD-RD | LCD-RD |

| LCD-CLK | LCD-DCLK | LCD-WR | LCD-WR | LCD-WR | LCD-WR | LCD-WR | LCD-WR |

| LCD-DE | LCD-DE | LCD-RS | LCD-RS | LCD-RS | LCD-RS | LCD-RS | LCD-RS |

| GPIO | / | / | / | / | CS | CS | CS |

| LCD-PWM | LCD-PWM | LCD-PWM | LCD-PWM | LCD-PWM | LCD-PWM | LCD-PWM | LCD-PWM |

| LCD-RST | LCD-RST | LCD-RST | LCD-RST | LCD-RST | LCD-RST | LCD-RST | LCD-RST |

8bit 带TE信号CPU 屏参考设计如图所示。

SPI屏支持以下几种模式:

| 3线1 Data | 3线2 Data | 4线1 Data | 4线2 Data | 2 Data Lane |

|---|---|---|---|---|

| DBI-CSX | DBI-CSX | DBI-CSX | DBI-CSX | DBI-CSX |

| / | / | DBI-DCX | DBI-DCX | / |

| DBI-SCLK | DBI-SCLK | DBI-SCLK | DBI-SCLK | DBI-SCLK |

| DBI-SDA | DBI-SDO | DBI-SDA | DBI-SDO | DBI-SDA |

| / | DBI-SDI | / | DBI-SDI | WRX |

| DBI-TE | DBI-TE | DBI-TE | DBI-TE | DBI-TE |

DBI接口与SPI1复用关系:

| DBI | SPI |

|---|---|

| DBI-CSX | SPI1-CS |

| DBI-SCLK | SPI1-CLK |

| DBI-SDO/SDA | SPI1-MOSI |

| DBI-SDI(WRX)/TE/DCX | SPI1-MISO |

| DBI-DCX/WRX | SPI1-HOLD |

| DBI-TE | SPI1-WP |

触摸屏电路设计

触摸屏设计要点如下:

- 使用V821芯片的TWI1与触摸屏进行通讯,此套TWI不建议与其他设备通讯。

- TWI上拉到VCC-IO,CTP-INT/CTP-RST 上拉到VCC33-PD。

- 注意确认触摸屏上的RESET信号上是否有对地1nf~100nf电容,若无电容,则触摸屏静电可能会比较差。

摄像头电路设计

V821支持一套MIPI-CSI 2lane 接口(支持拆分2套1lane MIPI-CSI接口)和1套并口CSI,其中MIPI-CSI从PA口引出,并口CSI从PD口引出,通过专用转接子板可支持双目摄像头输入。

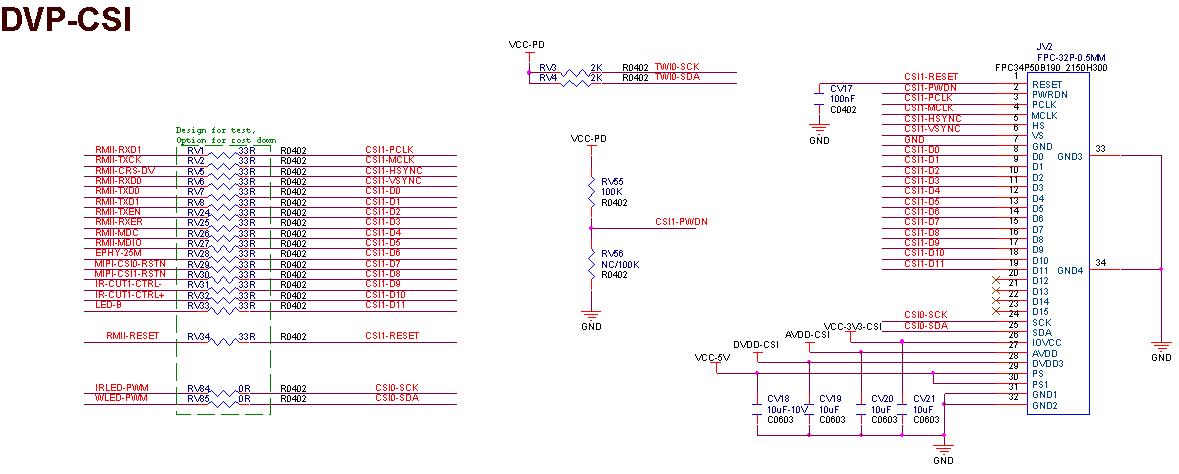

并口CSI设计注意事项如下:

- 注意根据SENSOR 的IO电平确定VCC-PA 的电压。

- 其他Sensor控制信号,如TWI/RESET/PWRDN等,建议使用PA口。当使用其他IO口时,主要电平匹配,当电平不一致时,需加电阻分压或者电平转换电路。

- MCLK 建议靠近座子端预留NC 电容,靠近SoC 端串接33R 电阻,用于降低时钟信号的EMI。

- SENSOR端的PCLK靠近SENSOR端预留NC电容,串接33R电阻,用于降低时钟信号的EMI。

- 为提升系统ESD性能,建议在sensor端的复位信号上预留100nF电容位置,靠近Sensor摆放。

- 摄像头TWI要加上拉电阻,注意检查是否有复用到其他IO,例如并口用了PA口的TWI0,则PC口的TWI0不能使用。

- 使用PD口作为并口CSI时,同上。

并口CSI参考设计如图所示。

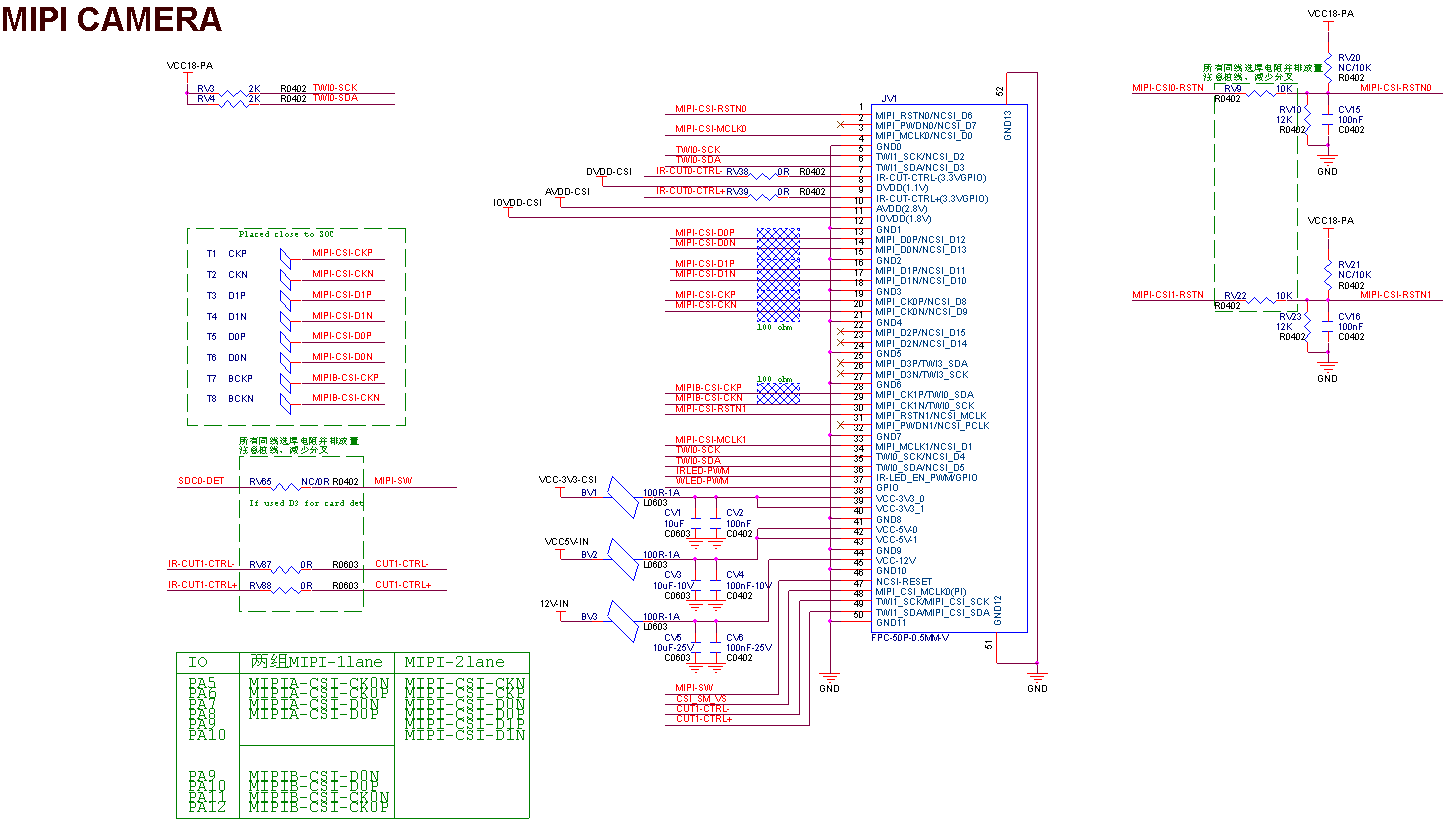

MIPI-CSI 设计注意事项如下:

- Sensor控制信号,如TWI/RESET/PWRDN等,建议使用PA口,采用1.8V供电,当使用其他IO口时,主要电平匹配,当电平不一致时,需加电阻分压或者电平转换电路。

- MCLK 建议靠近座子端预留NC 电容,靠近SoC 端串接33R 电阻,用于降低时钟信号的EMI 辐射。

- 摄像头TWI要加上拉电阻,注意检查是否有复用到其他IO,例如并口用了PA口的TWI0,则PD口的TWI0则不能使用。

- MIPI-CSI 支持2lane 拆分2*1lane,使用参考标案原理图设计。

MIPI CSI参考设计如图所示。

音频电路设计

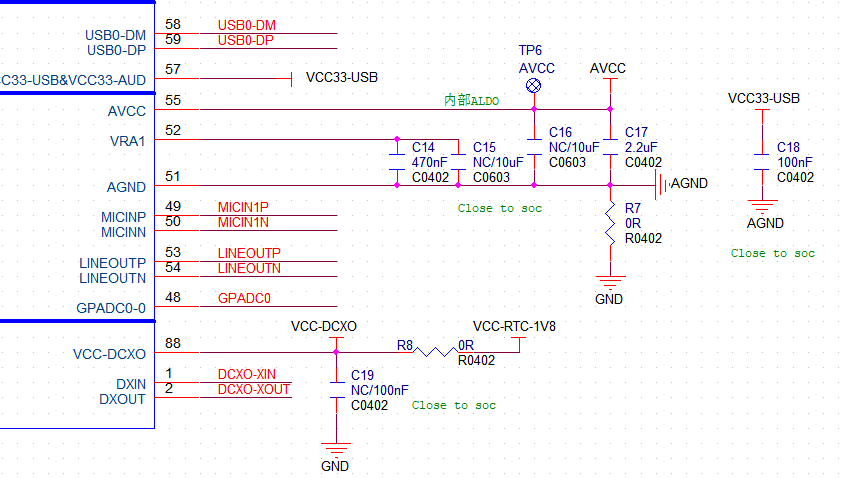

V821 Audio Codec音频设计建议如下:

- AVCC对地电容为2.2uF,VRA1对地电容为470nF,这些值不得随意更改。

- AVCC/VRA1/AGND通过0R电阻单点到地。

SoC音频电源部分设计如图所示。

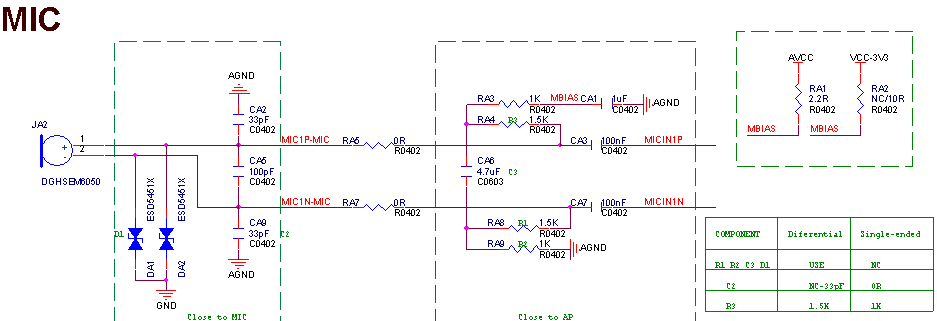

- MIC的电路设计使用类差分设计方案,为保证音频诗音质量,请勿修改该设计。

- MIC的偏置电阻需要根据MIC 的规格进行匹配,为了给MIC 输出信号提供一个正负半周最大动态范围,尽量保障MIC的输出端直流电压等于偏置电压MBIAS的一半。

- MIC输入端到SoC之间建议预留0R电阻方便debug ESD,阻值范围建议2.2R~5.1R,根据ESD测试结果确定所加电阻阻值。

MIC参考设计如图所示。

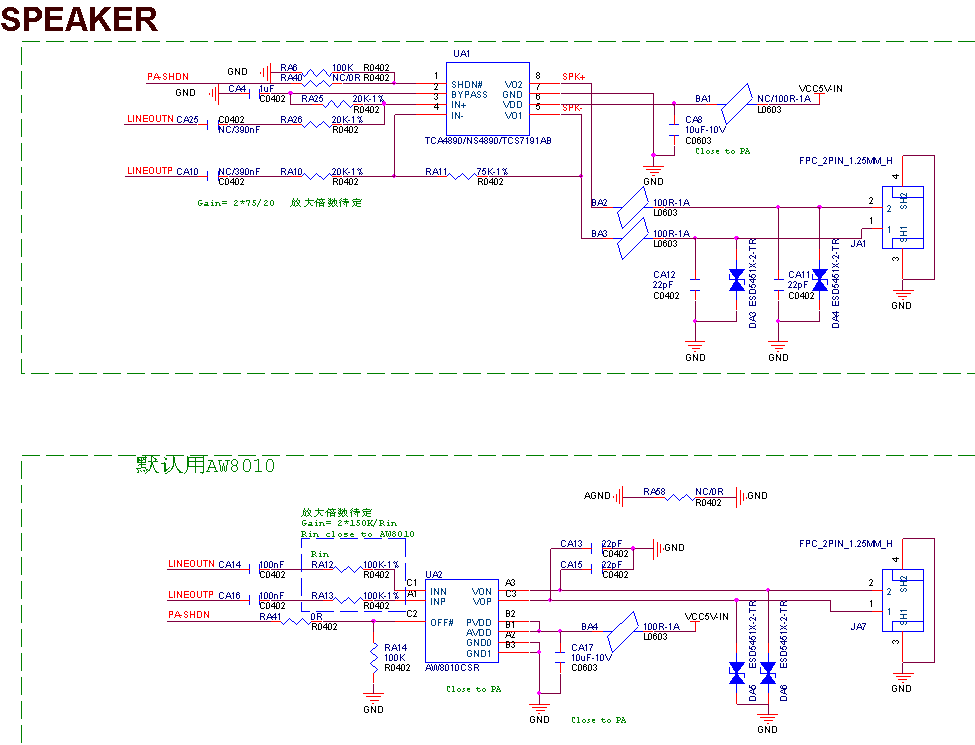

-

V821支持单喇叭输出,差分输出方式将功放默认接到LINEOUTP/N信号上, 同时将功放使能信号默认下拉电阻到地,避免上下电喇叭异响。功放设计时,注意反馈电阻的选用,反馈电阻的选用需参照功放的规格书,避免放大系数过大导致声音失真。

-

喇叭供电建议增加1R电阻提高ESD性能,同时将Audio PA与AGND连接降低其它因素干扰音频信号。

LINEOUT 作为SPEAKER差分输出电路如图所示。

- V821支持一套I2S接口,使用时注意SoC端DATA IN/OUT反接,即I2S-DIN接外设的DOUT如BT-PCM-OUT, I2S-DOUT接外设的DIN如BT-PCM-DIN。

数字音频功能需要使用I2S功能,若产品应用上需要该功能,请联系全志FAE。

ADC电路设计

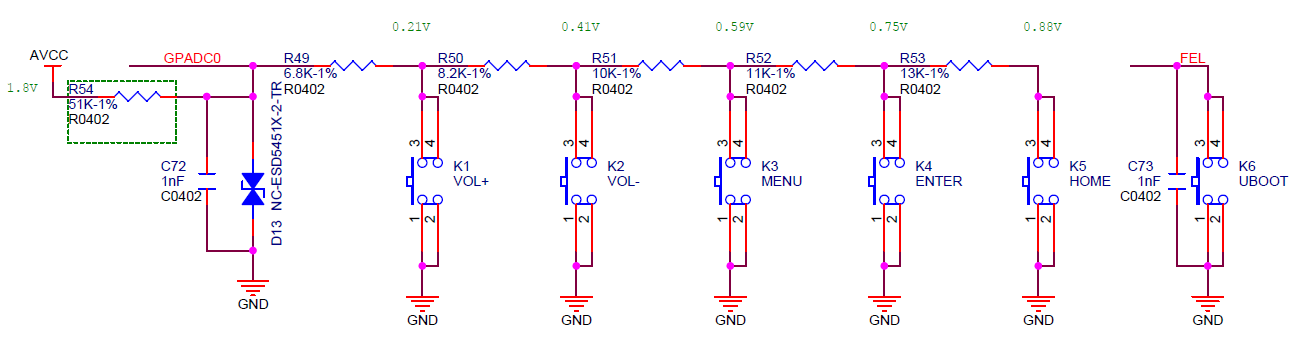

V821芯片支持3套GPADC接口,采样位数为12-bit,有效位为8-bit,最大采样率为1Mhz,可以用来做按键功能和检测电池电压功能,耐压为1.8V。

ADC 设计建议如下:

- 按键分压电阻,请使用推荐的阻值,推荐使用1%精度电阻。添加按键时保证按键按下后,GPADC网络电压范围为0~1.8V,检测精度为0.12V,即两按键间压差为0.12V以上。

- GPADC 按键键数选择,根据产品需要进行增加或者删减。如果不需要按键,若考虑SDK 兼容,则GPADC 必须加51K 上拉电阻到AVCC,否则GPADC0可以floating。

- GPADC作为对外接口如按键使用时,接口到主控端需串接K级电阻。

- RESET、POWER 按键请根据产品需求进行删减。

- UBOOT 按键为硬件触发烧写程序按键,请根据产品需求决定是否预留。

- 全志烧写程序的方式有两种,请务必保证其中一种烧写更新固件方案,避免机器程序被破坏后无法软件烧录的情况。

- UBOOT按键通过USB口烧写固件;

- PC口 CARD固件升级方式;

按键推荐电路如图所示。

- AXP2601作为电池电量检测功能使用,若不使用该电量计,可以采用分压电阻电路,电阻阻值不得随意更改。

ADC电池电量检测推荐电路如图所示。

Wi-Fi/BT电路设计

V821M2-WXX内部集成Wi-Fi,可省去外挂Wi-Fi芯片。若需外挂Wi-Fi/BT模组,部分设计要点如下:

- Wi-Fi模组SDIO电平要与PD口电平保持一致。

- Wi-Fi 模组接相关唤醒中断控制建议接到PD口,若接到其他组IO,需注意电平匹配问题。

- SDIO的CLK上需要串接27nF电感,并要并接一个5.6pF电容到地,降低CLK上的辐射干扰,因为SDIO的CLK本身也是会干扰Wi-Fi。

- 主控端UART TX/RX/CTS/RTS信号必须与模组端信号交叉连接,主控端PCM IN/OUT信号必须与模组端信号交叉连接。

BT模块UART和I2S连接关系如表所示。

| 主控端 | BT 端 | 主控端 | BT 端 | |

|---|---|---|---|---|

| UART-RX | UART-TX | PCM-CLK | PCM-CLK | |

| UART-TX | UART-RX | PCM-SYNC | PCM-SYNC | |

| UART-RTS | UART-CTS | PCM-DOUT | PCM-DIN | |

| UART-CTS | UART-RTS | PCM-DIN | PCM-DOUT |

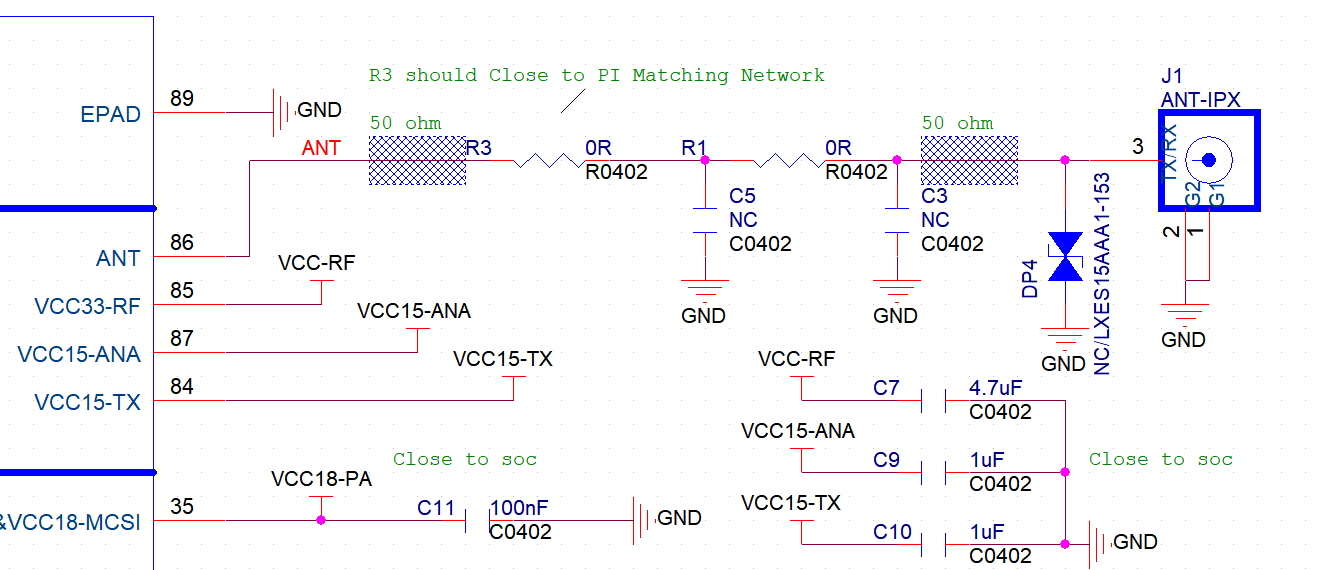

- Wi-Fi的天线设计建议预留π型匹配电路,便于天线的匹配调试。天线匹配参考设计如图所示。

- 外挂 WIFI 模组天线匹配参考设计如图所示。

对于其它不同厂家的Wi-Fi模组,具体原理设计请参照Wi-Fi原厂的设计指导文档。

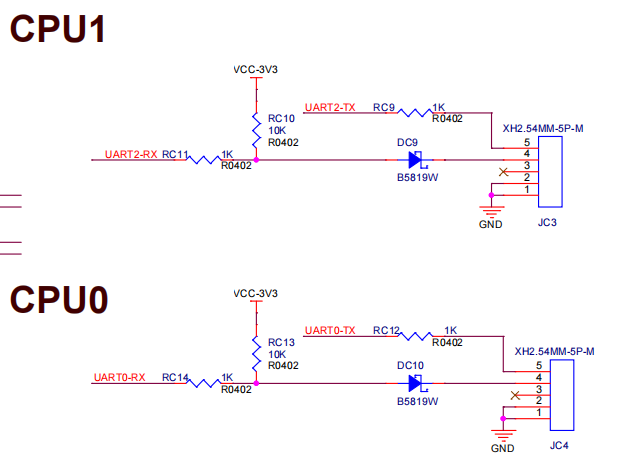

UART

CPU0、CPU1的调试接口UART需要保留,以便开发调试。量产可以不贴元件,但尽量保留测试点,增加量产问题的分析调试方法。UART 接口建议增加防漏电电路,避免样机在长期老化测试中样机和电脑之间存在漏电,导致机器工作不正常或者电脑被拉挂,二极管压降要求小于1V,避免电平识别错误。串口RX和TX建议串接1K电阻,提高ESD性能,防止连接电脑串口时静电损坏串口PIN。

UART电路参考设计如图所示。

调试阶段 UART 接口必须增加防漏电电路,否则会导致下列问题:

- MMC 无法认卡,打印如下日志

[ 43.191637] sunxi:sunxi_mmc_host-44020000.sdmmc:[ERR]: smc 0 p0 err, cmd 13, RD DTO !!

[ 43.200614] sunxi:sunxi_mmc_host-44020000.sdmmc:[INFO]: retry:start

[ 43.207654] sunxi:sunxi_mmc_host-44020000.sdmmc:[ERR]: retry:stop

[ 43.214591] sunxi:sunxi_mmc_host-44020000.sdmmc:[ERR]: retry:stop recover

[ 43.222581] sunxi:sunxi_mmc_host-44020000.sdmmc:[INFO]: REG_DRV_DL: 0x00010000

[ 43.230703] sunxi:sunxi_mmc_host-44020000.sdmmc:[INFO]: REG_SD_NTSR: 0x81710000

[ 43.238936] sunxi:sunxi_mmc_host-44020000.sdmmc:[INFO]: *****retry:re-send cmd*****

[ 43.247517] sunxi:sunxi_mmc_host-44020000.sdmmc:[ERR]: smc 0 p0 err, cmd 13, RD RTO !!

[ 43.256411] sunxi:sunxi_mmc_host-44020000.sdmmc:[INFO]: retry:start

[ 43.263460] sunxi:sunxi_mmc_host-44020000.sdmmc:[ERR]: retry:stop

[ 43.270354] sunxi:sunxi_mmc_host-44020000.sdmmc:[ERR]: retry:stop recover

[ 43.278788] sunxi:sunxi_mmc_host-44020000.sdmmc:[ERR]: send manual stop command failed 100

- TF 卡容量识别错误,例如下面的 32G 卡识别成 121M 卡

[ 44.728899] mmc0: new SD card at address 0001

[ 44.734559] mmcblk0: mmc0:0001 121 MiB

- 外围 RTC 漏电,RTC 时间错误

- DCDC 灌电,上电时序错误

如果发现以上无法认卡的情况,可以尝试更换防灌电的串口,也可以拔掉串口的 TX,也就是 SoC 那边的 RX,防止灌电进入开发板,再测试问题是否存在。

TWI

- PD口TWI1为主控与CTP专用TWI通讯总线,不建议与其他TWI设备共用。

- TWI 最大支持400Kbit/s的传输速率,总线上加上拉电阻,推荐值为2.0K~2.2K,上拉电源为对应GPIO电源域,各设备地址不得有冲突。

- TWI 若加了电平转换电路,建议配置为100Kbit/s的传输速率。

- TWI 推荐使用参考设计分配,注意同一套TWI有可能可以从PA/PC/PD/PL口引出,设计只能用其中一组。

GPIO&特殊管脚说明

- GPIO分配建议按照标案图进行设计,请勿随意调整,降低软件适配工作量。

- GPIO分配时,请确保电平相匹配,上拉的电压域必须为此GPIO的电源域,以防外设向SoC漏电情况发生。如PC口的上拉电阻必须上拉到VCC33-PC口。所有原理图,此项是必检查项目。

- 具有独立电源引脚的GPIO,可以根据外设需求进行电压的适配调整,如PC,PD等,全志PA口一般由VCC-IO 供电默认1.8.V,使用时注意外设电平匹配问题

- V821平台GPIO电源域如下表所示。

| GPIO 分组 | 控制电源域 | IO电源域 | IO电压 | 备注 |

|---|---|---|---|---|

| PA | VDD-SYS | VCC-PA | 1.8V | 若MIPI-CSI MCLK和TWI信号用PA口,则固定为1.8V供电 |

| PC | VDD-SYS | VCC33-PC | 3.3V | |

| PD | VDD-SYS | VCC33-PD | 3.3V | |

| PL | VDD-SYS | VCC33-PLVCC18-PL | 1.8/3.3V | PL0、PL1固定电平1.8VP2-PL7默认电平3.3V,可配置为1.8V |

- PC口因在启动过程中有初始化启动介质的操作,初始化过程中IO会有高电平脉冲信号,所以不建议PC口当做指示灯、喇叭或外设供电使能等功能使用。

- 若外设对GPIO比较敏感且影响用户体验的功能模块控制IO如指示灯控制、喇叭功放使能等建议在相应控制IO增加下拉电阻,解决上电指示灯闪和上电喇叭爆破音。

- 对于这一组有未使用的IO则建议该不用的IO浮空处理。

- V821 部分GPIO有集成上下拉电阻,可通过软件配置,各组GPIO上下拉电阻如表所示。

| GPIO 分组 | 上下拉电阻 | 精度 |

|---|---|---|

| PC0-PC16 | 15K | ±20% |

| PD1、PD2、PD4、PD5、PD6 | 33K | ±20% |

| 其他 GPIO | 100K | ±20% |

设计指南未涉及模块请查阅datasheet,具体应用案里的关键电路若有疑问的请联系全志FAE。

PCB设计

叠层设计

V821可以采用2层板设计也可采用4层板设计。

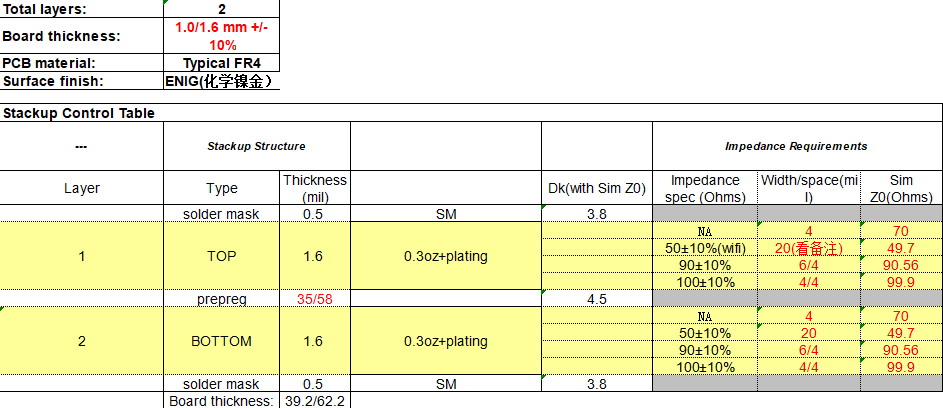

- 2层板整体采用TOP BOTTOM叠层结构

2层板厚0.8~1.6mm叠层设计参考如图所示。

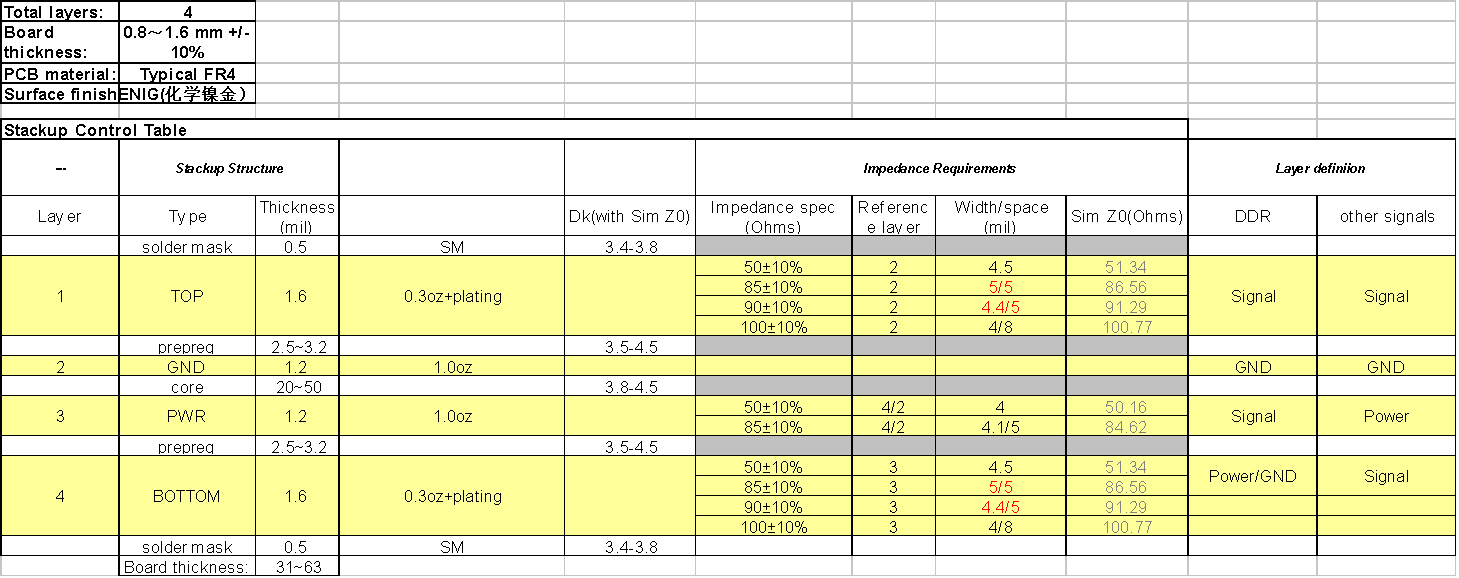

- 4层板整体采用SGSP叠层结构

4层板厚0.8~1.6mm叠层设计参考如图所示。

若PCB层数或者叠层结构与全志叠层不一致时,需要重新计算各走线是否满足阻抗要求。并联系全志FAE进行检查确认。

小系统LAYOUT建议

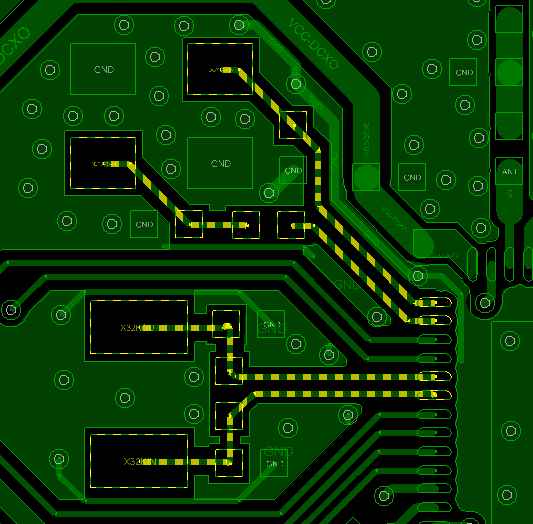

系统时钟LAYOUT设计

DCXO时钟和32K时钟建议LAYOUT采用以下原则:

- 晶振尽量靠近IC摆放,使DCXO-XOUT/DCXO-XIN、X32KOUT/X32KIN走线小于600mil,减少PCB走线寄生电容,保证晶振频偏精度。

- 晶振的匹配电容必须靠近晶振管脚摆放。

- 晶振及其走线区域的外围和相邻层,用GND屏蔽保护,禁止其它走线。

系统时钟走线layout参考如图所示。

SoC电源LAYOUT设计

SoC端电源建议LAYOUT采用以下原则:

- SoC 端电源fanout建议按照全志模板来,SYS/DRAM/VCC-RF三路大电流电源以铺电源平面实现,SYS布线最窄处要求有1A的通流能力,VCC-RF布线最窄要求有500mA通流能力。

SYS/DRAM/VCC-RF两路大电流电源平面如图所示。

- VCC-RF 电源走线,需要避免开关时钟等敏感信号。

- 各路电源电容需靠近SoC放置,放置距离要求小于去耦半径。

- VBAT-RTC/VCC-RF/AVCC等敏感电源电容靠近SoC pin脚放置。

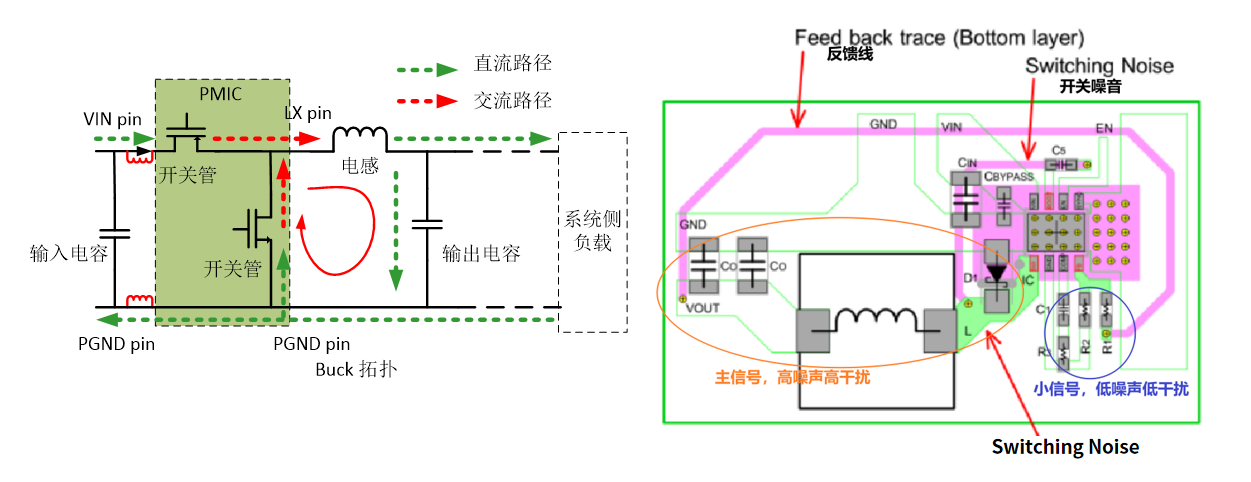

电源LAYOUT设计

DCDC电源建议Layout 采用以下原则:

- 先重点关注反馈环(FB脚),反馈线不要走肖特基二极管、电感、大电容下面,不要被大电流环路包围,必要时可在取样电阻(上端电阻)并100PF-10NF的电容,增加稳定性,但瞬态会受一些影响。

- 反馈线宁可细不要租,因为线越宽,天线效应越明显,影响环路稳定性,一般可用6-12mil线(英寸),可布置在地层,周边接地覆铜包围。

- 所有电容尽可能接近IC(芯片)。电容如用贴片陶瓷电容MLCC,比如计算22uF,拆成两个10uF并联更好。输出电容如果用铝电解,千万记得用高频低阻的,不可以随便放个低频滤波电容。

- 尽可能缩小大电流环路的包围面积(也就是结构紧凑些)。如果不方便,用覆铜的方式变成一条窄缝。

- 输入电容Cin的GND和输出电容Cout的GND保持1CM-2CM距离,否则输入端高频干扰可能通过Cout耦合进输出。

- 电感下方不要走线,引脚之间挖空,不要使用大面积的铜皮,电感两个贴片引脚不要靠太近,避免寄生电容将开关噪声引至输出电容。

- 电感节点走线至少20mil,条件允许可以铺铜,改善散热。如果用了半屏蔽/非屏蔽电感,输出电容要离远一些。

- 芯片底部有大面积裸露引脚,焊盘上要引入散热过孔分布,建议用0.3mm过孔,内孔用12mil外24mil。

- 输入输出电容周围增加过孔,使其良好接地。在一个厚度d=20mil线路板上,同向电流过孔(过孔在同一块铜皮上)的间距应大于过孔长度,即S1>d(20mil).反向电流过孔(过孔在不同的铜皮上)的间距应小于过孔长度,即S2<d(20mil)。

- 电源layout布局参考如图所示。

eMMC LAYOUT 设计

eMMC 建议 Layout 采用以下原则:

- eMMC应靠近主控摆放,去耦电容均靠近eMMC电源管脚摆放。

- VCC/VCCQ线宽不小于12mil,或直接使用敷铜代替电源走线;电源线上如有过孔,则换层处过孔数量不少于2个,避免过孔限流影响供电。

- eMMC-CLK信号串接电阻靠近主控摆放,串阻与主控连接走线距离≤300mil。

- eMMC与主控走线间走线≤2000mil,走线路径上尽量少打过孔,不超过3个。

- 信号线阻抗控制50ohm,线间距不小于2倍线宽。

- D0~D7、DS相对CLK等长控制≤300mil。

- 走线尽量避开高频信号,务必保证走线参考平面完整。

- CLK和DS信号做包地处理,包地通过过孔与GND平面连接,如果不能包地则保持线间距≥3倍线宽。

- eMMC NC/RFU等保留引脚都悬空,不可为了走线方便将这些信号与电源、地、或其他eMMC信号连接在一起。如果确实走线有困难,可适当修改eMMC PCB封装,去掉一些NC/RFU的ball。

SD Card LAYOUT设计

CARD 建议Layout 采用以下原则:

- CLK串接电阻靠近主控摆放,串阻与主控CLK连接走线距离≤300mil。

- VCC-CARD网络上的电阻和电容网络靠近卡座摆放,VCC-CARD走线宽度不小于12mil。

- 信号线阻抗控制50ohm,长度小于10CM,线间距不小于2倍线宽,D0~D3相对CLK等长控制<500mil。

- 走线尽量避开高频信号,信号线走线参考平面完整。

- CLK做包地处理,包地通过过孔与GND平面连接。如果不能包地则保持线间距≥3倍线宽。

- ESD器件靠近卡座放置,卡座管脚走线先经过ESD器件,再连其它器件。

- 卡座外壳接地要充分。

SDIO LAYOUT设计

SDIO 建议Layout 采用以下原则:

- CLK串接电阻靠近主控摆放,串阻与主控CLK连接走线距离≤300mil。

- 信号线阻抗控制50ohm,长度小于10CM,线间距不小于2倍线宽,D0~D3相对CLK等长控制<500mil。

- 走线尽量避开高频信号,信号线走线参考平面完整。

- CLK做包地处理,包地通过过孔与GND平面连接。如果不能包地则保持线间距≥3倍线宽。

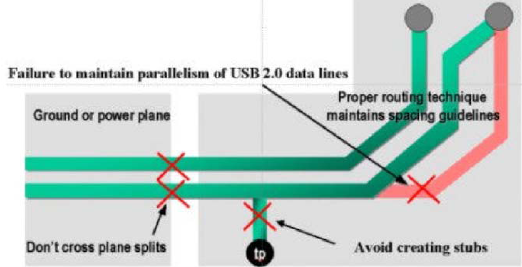

USB LAYOUT设计

USB建议Layout 采用以下原则:

- VCC33-USB走线线宽8~12mil,VCC33-USB的0.1uF电容,需要靠近IC摆放。

- USB-DM/USB-DP信号差分走线,差分阻抗为90ohm,保证走线参考层不跨分割。

- USB-DM/USB-DP建议与其它信号的间距大于10 mil,避免走线走在器件下面或者与其他信号交叉。

- USB-DM/USB-DP走线在有空间的情况下,走线两边包地并打地过孔。

- USB-DM/USB-DP走线拐角的角度需保证大于等于135度;保证USB走线的长度控制在4000mil以内,走线的过孔不超过2个。

- TVS器件需要靠近USB座子摆放。

- USB座子金属外壳接地管脚建议TOP面建议全铺接地,其他层也建议充分接地。

USB走线参考如图所示。

显示屏LAYOUT设计

RGB LAYOUT设计

RGB 建议Layout 采用以下原则:

- 信号线上串接电阻建议靠近座子放。

- LCD走线尽量满足3W原则,如不能,则至少要满足2W原则。

- LCD-CLK要做包地处理,同时要注意对包地打孔。

- LCD线的参考平面要完整。

- 背光电路要求:PS,VLED+,VLED-所在的网络的线宽要在20mil以上。

CSI LAYOUT设计

CSI 建议Layout 采用以下原则:

- AVDD,IOVDD和DVDD的滤波电容靠近模组放置。

- MCLK的对地电容及串联电阻靠近主控,PCLK串接电阻靠近sensor端。

- MCLK需要包地走线,如果PCB空间有限,不能保证信号线完整包地时,需保持该信号线在间距≤15mil空间内无其他走线。

- NCSI_PCLK需要包地走线,如果PCB空间有限,不能保证信号线完整包地时,需保持该信号线在间距≤15mil空间内无其他走线。

- MIPI差分走线需要100ohm阻抗匹配,优先走线,走线尽量短,少换层。

- 差分对内等长10mil,对间等长≤300mil(越小越好)。

- 为减小差分对间干扰,各差分对间用地线隔开,或保持间距≥15mil。

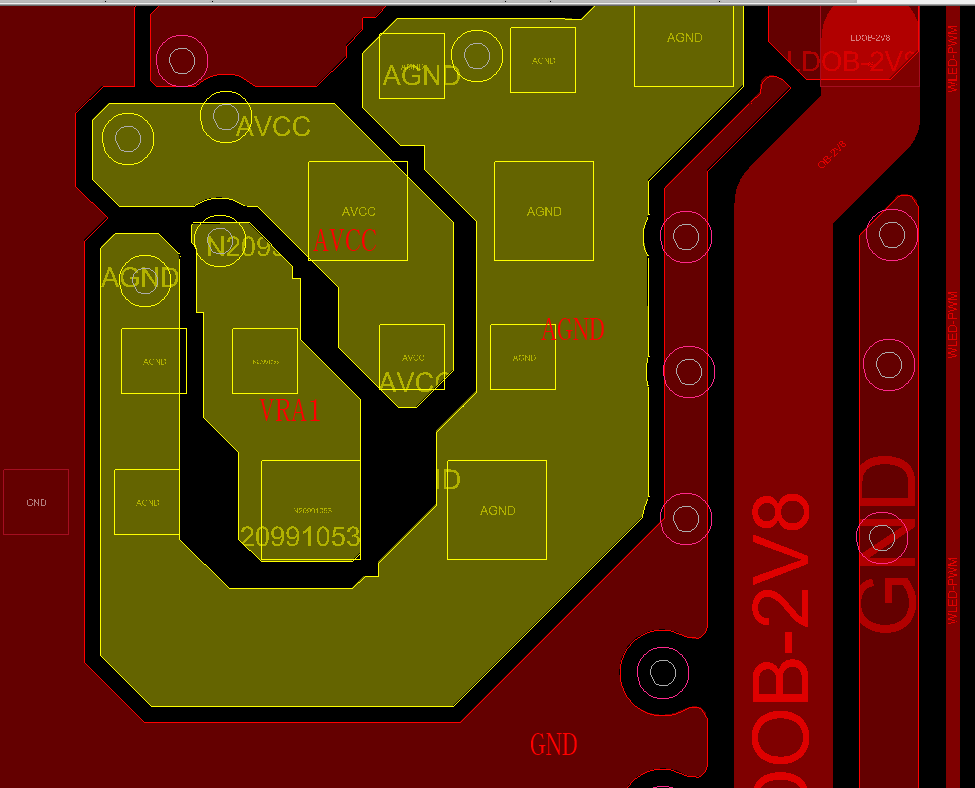

音频LAYOUT设计

SoC端音频部分建议Layout 采用以下原则:

- AVCC/VRA1/AGND接地电容、电阻依次靠近主控摆放。

- AVCC 和其他电源合并时,layout 注意和其他合并的电源采用分支走线,减小其他电源对AVCC的干扰。

- PCB走线AVCC线宽≥10 mil;VRA1线宽≥10 mil;线长≤300mil。

- AGND需有一片覆铜,覆铜宽度≥20mil,AGND接地电阻连接到GND平面的过孔≥2个。

AVCC/VRA1/AGND走线参考如图所示。

MIC 建议Layout 采用以下原则:

- MIC 外围器件位置按照原理图要求摆放。

- MICxP/MICxN,类差分走线,线宽4mil、线距4mil,包AGND地。

- MIC走线及摆放位置远离(>=200mil)RF、PA、开关电源。

- MBIAS与MICxP/MICxN并行走线,线宽10mil。

- ESD 器件必须靠近MIC摆放,从MIC引出来的走线必须先经过ESD器件,在连接其他器件。

- LINEOUTP/N每对P、N信号分别类差分走线,线宽4mil,线距4mil,包地。

- MIC/LINEOUT除了包地之外建议增加AGND参考地层,以保证音频信号质量。

Wi-Fi和天线LAYOUT设计

Wi-Fi 建议Layout 采用以下原则:

- 模组尽量靠近天线或天线接口。远离电源、DDR、LCD电路、摄像头、马达、SPEAKER等易产生干扰的模块。

- SDIO的走线参考SDIO部分的layout设计要求。

- 天线馈线控制50ohm,为了增大线宽减少损耗,通常馈线相邻层挖空,隔层参考参考平面需要是完整地,同层地距离天线馈线距离保持一致,两边多打地过孔,地过孔需要回到芯片EPAD。

Wi-Fi 天线地回路参考设计如图所示。

- 射频线需要圆滑不要换层,并进行包地处理,两边均匀的打地过孔,射频线需要远离时钟线的干扰。

- 合理布局天线馈线的匹配电容电阻,使馈线平滑,最短,无分支,无过孔,少拐角。

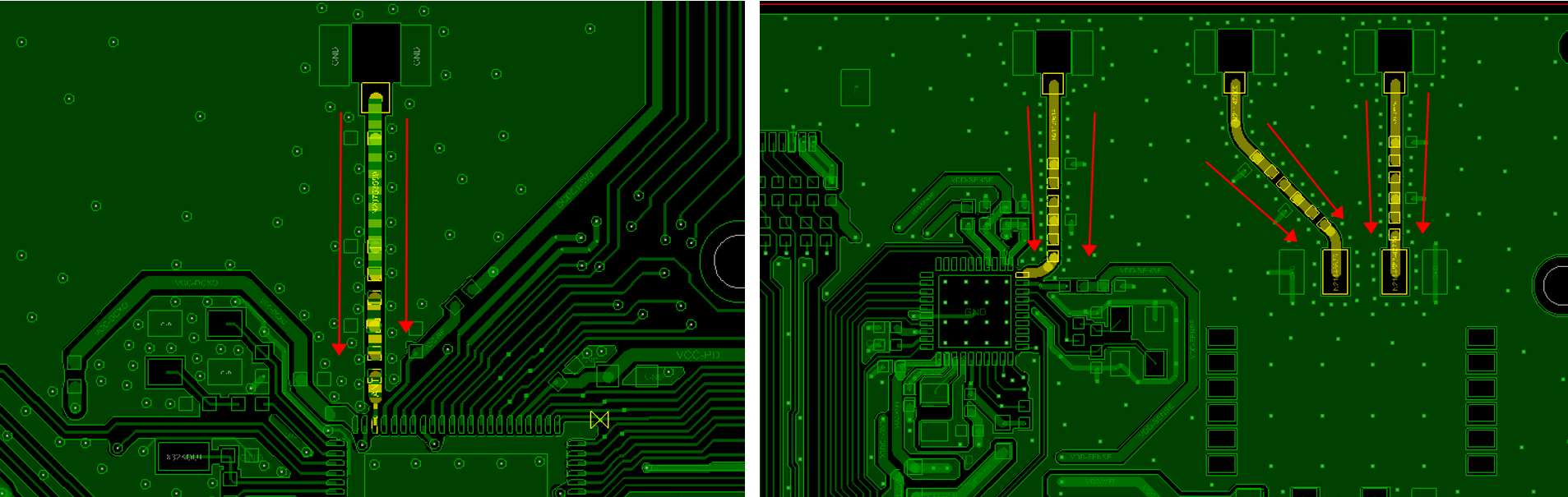

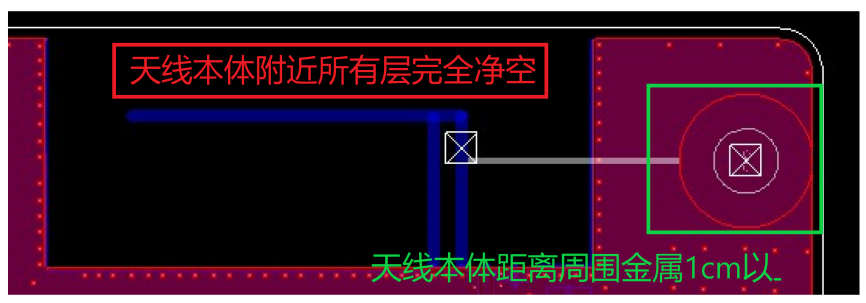

- 如使用PCB走线作天线,请确保天线走线附近区域完全净空,净空区大于50mm²,天线本体至少距周围的金属1cm以上。

Wi-Fi 板载天线LAYOUT参考

EMC 设计

产品ESD测试经常遇到LCD花屏、卡机、TP触摸失灵、系统崩溃等问题。产品的ESD问题与结构工艺设计、电子系统设计、软件设计、元器件选型等密切相关。如果产品对ESD性能要求较高,为了减少产品开发周期,产品设计之初要考虑到ESD设计。主要从原理图设计、PCB设计、结构工艺、软件几个维度上提前做好设计。

原理图ESD设计

原理图ESD设计建议参考如下:

- 系统挂死与IO的抗ESD能力有关,提高各接口输入PIN的ESD能力有助于提高系统ESD。

- 如USB-ID/CARD-DET等检测PIN,将其到SoC端串接电阻有利于提高ESD性能。

- 各接口均要根据接口类型在电源和信号上预留合适的ESD保护器件。

- GPADC 使用按键或者光敏检测时,到SoC端要串接K级电阻,提高ESD性能。

- MIC输入到SoC之间建议预留串接5.1R电阻,并在MIC座子端预留ESD器件,提高ESD性能。

- 对于摄像头、显示屏、TP触摸屏上的reset信号,需在模组上靠近芯片管脚的位置增加1~100nF电容接地。

- 关键敏感电源采用LC/RC滤波设计,如PA电源端串1R电阻提高喇叭IC的ESD性能。

- 部分与外部直连或者裸露的接口,如speaker、MIC、USB、TF、按键等,必须加上合适的ESD器件。

- 部分电路增加独立电源开关支持软件复位,如加上Card 供电开关可以执行软件复位Card操作。

PCB ESD设计

PCB ESD设计建议参考如下:

- PCB层叠设计必须保证不少于1L完整的GND平面,所有的ESD泄放路径直接通过过孔连接到这个完整的GND平面;其他层尽可能多的铺GND。

- POWER平面要比GND平面内缩不少于3H(H指POWER平面相对GND平面的高度)。

- 在PCB四周增加地保护环;DDR线束四周建议用GND保护。

- 关键信号(GPADC/NMI/Clock等)与板边距离不小于5mm,同时必须与走线层的板边GND铜皮距离不小于10mils。

- CPU/DRAM/晶振等ESD敏感的关键器件,离外部金属接口的距离不小于20mm,如果小于20mm,建议预留金属屏蔽罩,并且距离其他板边不小于5mm。

- 关键信号(GPADC/NMI/Clock等)尽量避免与外部接口信号(USB/SD等)或经过IO附近的走线相邻并行走线;如果不可避免,相邻并行的走线长度不超过100mils;IO保护地下方尽量不要走线,在必须走线的情况下建议走内层。

- 无论外部接口信号还是内部信号,走线避免多余的桩线。

- 必须保证外部连接器(USB/SD)金属外壳接地良好,在板边直接通过过孔连接GND平面,每个GND焊盘与GND平面之间的连接过孔不少于3个。

- 对于部分ESD整改难度较大的IO,可将IO GND独立出来,与主GND用磁珠连接以防止静电能量进入主GND(需在信号质量可接受的范围内)。

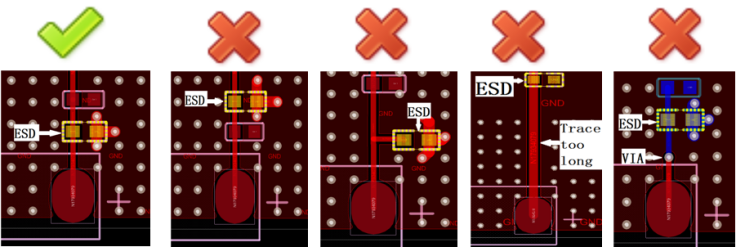

- 外部接口信号(USB/SD/HP)必须连接外部ESD器件,进行ESD保护。如下图所示,外部接口信号ESD器件放置位置尽可能靠近外部连接器,与连接器间避免过孔;ESD器件接地端直接通过过孔连接到GND平面,而且过孔数量不少于3个;从外部接口进来,必须最先看到ESD器件;ESD器件的信号端与外部信号端必须尽可能短,尽可能宽,建议直接搭接在信号走线上。

软件ESD措施

软件ESD措施如下:

- 把不用的IO口设置为低电平。

- 加看门狗,对保护的目标状态位进行检测。

- 出现LCD花屏、卡顿、卡死等异常现象时,如果在硬件整改无效的情况下,可以考虑增加LCD软复位的策略。

- 出现TP失灵,不能恢复正常时,在硬件整改无效的情况下,可以考虑增加TP软复位的策略。

- 出现Card 读写失败时,执行Card掉电上电进入录像操作。

结构ESD措施

结构ESD措施如下:

- 整机结构、装配工艺设计时,可通过加大PCBA的GND平面与外部金属平面的有效接触面积,如LCD金属保护壳,增加ESD的泄放平面,提升ESD水平。

- 如果整机有接口副板设计,通过FPC排线与主板连接,建议将接口ESD器件摆放在副板上,并将副板与LCD金属平面通过导电棉有效连接在一起,使其就近下地,降低ESD流入主板干扰到SoC系统工作。

- 建议在PCB板双面四周均匀留出多个不小于25mm2的GND裸露铜皮(此铜皮直接通过过孔与GND平面相连),并通过导电棉与金属平面相连接。

- 塑胶内层喷导电漆,并将其与GND平面有效连接,达到屏蔽的效果。

- 如果LCD的FPC排线过长易受干扰,可以将FPC排线贴导电布屏蔽,或者采用屏蔽的FPC排线。

- LCD在ESD测试异常时,可能是LCD的TCOM板电路受到干扰导致,可以考虑将其贴导电布屏蔽。

- 整机在结构工艺设计时,尽量将LCD、TP等ESD敏感部件远离裸露在外面的金属接口,降低ESD干扰风险。

- 把端口的地与金属壳相连接而加大ESD的泄放空间。

- 如果结构允许,建议增加屏蔽罩,对关键电路进行屏蔽,同时必须保证屏蔽罩的各边良好接地;(避免屏蔽罩电荷积累,对内部信号放电)。

- 整机装配时,需确保PCBA与LCD平面有效的接触,增加ESD泄放路径。

- 在SD card和显示屏之间增加导电棉,增强抗静电水平。