DRAM 基础知识

什么是DRAM

DRAM(Dynamic Random Access Memory,动态随机存取存储器)是计算机系统中的主存储器,负责存储正在运行的程序和数据。

DRAM的基本工作原理

存储单元结构:

- 1个晶体管 + 1个电容(1T1C结构)

- 电容存储电荷:有电荷=1,无电荷=0

- 晶体管作为开关,控制读写操作

为什么叫"动态"?

- 电容会漏电,电荷只能保持几毫秒

- 必须定期刷新(Refresh)来补充电荷

- 典型刷新周期:64ms内刷新所有行

- 刷新操作会占用带宽,影响性能

读写过程:

- 读操作:激活字线 → 打开晶体管 → 检测位线电压变化 → 放大并输出

- 写操作:激活字线 → 打开晶体管 → 对电容充电或放电

- 刷新:读取每行数据并重新写入,防止数据丢失

与其它存储器的对比

| 存储类型 | 结构特点 | 是否需要刷新 | 速度 | 密度 | 成本 | 应用场景 |

|---|---|---|---|---|---|---|

| DRAM | 1T1C | 需要 | 中 | 高 | 低 | 主存(系统内存) |

| SRAM | 6T | 不需要 | 快 | 低 | 高 | CPU缓存 |

| Flash | 浮栅晶体管 | 不需要 | 慢 | 高 | 中 | 存储(SSD、U盘) |

DDR技术演进

DDR = Double Data Rate(双倍数据速率)

- 传统SDR:每个时钟周期传输1次数据

- DDR:在时钟的上升沿和下降沿都传输数据,带宽翻倍

技术演进路线:

| 代际 | 典型速率 | 工作电压 | 主要改进 |

|---|---|---|---|

| DDR3 | 800-2133 MT/s | 1.5V | 8位预取 |

| DDR4 | 1600-3200 MT/s | 1.2V | Bank Group、更低功耗 |

| DDR5 | 3200-6400+ MT/s | 1.1V | 双通道、更高密度 |

| LPDDR4/5 | 3200-6400+ MT/s | 1.1V | 低功耗设计、移动设备优化 |

LPDDR的特点:

- Low Power DDR,专为移动设备设计

- 更低的工作电压和待机功耗

- 通常焊接在PCB上(PoP封装),不使用DIMM插槽

为什么学习DRAM基础知识?

- DRAM是嵌入式系统的核心组件,直接影响系统性能

- 理解DRAM架构有助于系统调试和性能优化

- 存储子系统故障是常见的硬件问题,需要基础知识支撑排查

- DRAM选型、适配需要掌握容量、带宽等关键参数

了解了DRAM的基本概念后,我们来看DRAM子系统的整体架构。

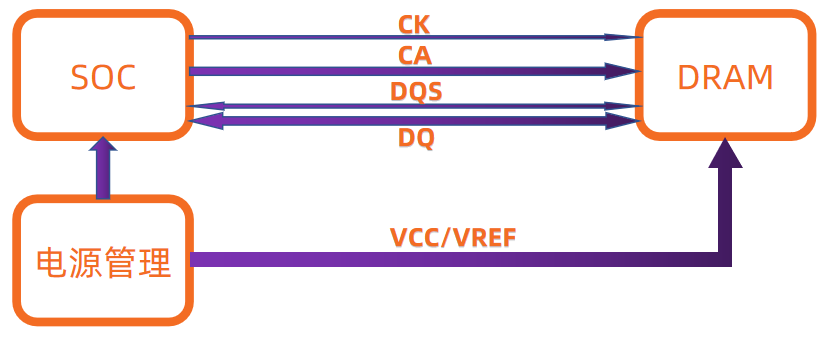

DRAM子系统

DRAM子系统是整个内存系统的完整架构,由多个组件协同工作,共同实现数据的存储与访问。

组成结构

DRAM子系统由以下四个核心部分组成:

| 组件 | 说明 | 关注重点 |

|---|---|---|

| 主控SOC | 包含控制器和PHY,通常称为DDR IP | 控制逻辑、时序参数 |

| 传输链路 | 基板、PCB走线等信号通路 | 信号质量、极限性能 |

| DRAM颗粒 | 数据的实际存储载体 | IO性能、稳定性 |

| 电源 | 为各组件供电 | 直流压降、纹波系数 |

各组件角色

主控SOC:SOC内的DRAM子系统包含控制器和PHY,是整个子系统的控制核心。

传输链路:通常包含基板、PCB走线等,影响信号质量,与子系统的极限性能有直接关系,设计与制造均需要关注。

DRAM颗粒:占子系统成本的主要部分,其IO性能以及存储单元稳定性是主要关注点。

电源:容易忽略的部分,主要关注路径直流压降以及应用端的纹波系数。

DRAM子系统中的核心组件是DDR IP,它负责管理与DRAM颗粒的所有通信操作。下一节我们将深入了解DDR IP的内部结构。

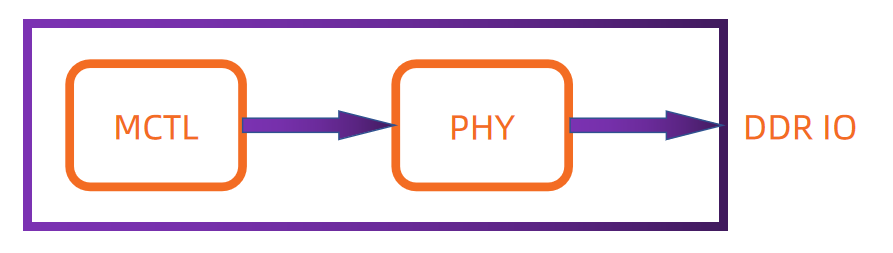

DDR IP

DDR IP是DRAM子系统的核心处理单元,位于SOC内部,负责与DRAM颗粒的所有通信操作。

组成结构

DDR IP由两个主要部分组成:控制器(Controller)和物理层(PHY)。

控制器(Controller)

角色:整个子系统的指挥中心,所有控制/操作命令的发起者。

主要职责:

- 接收CPU/总线的内存访问请求

- 管理命令队列和调度

- 发起所有控制/操作命令

- 控制时序参数和电源管理

- 决定子系统的性能、功能和稳定性

PHY(物理层)

角色:连接DDR控制器和DDR颗粒的桥梁。

主要职责:

- 将控制器发出的数据转换为符合DDR协议的信号,发送到DRAM颗粒

- 将DRAM发送的数据转换为符合DFI协议的信号,传送给控制器

- 处理读写时序对齐

- 管理信号完整性

DDR IP与DRAM颗粒之间的通信通过传输链路完成,链路设计的质量直接影响系统的信号完整性和最高工作频率。

传输链路设计

DDR IP与DRAM颗粒之间通过传输链路连接,链路设计决定了信号质量和系统能达到的最高频率。

设计内容

DRAM子系统链路设计覆盖高速信号设计的各个关键点,主要包括:

- DIE内设计:芯片内部的信号布线

- 基板设计:封装基板的信号走线

- 封装ball设计:芯片封装的球栅阵列布局

- 原理图设计:电路原理图设计

- PCB设计:印刷电路板走线设计

设计要点

以上设计是构建高性能内存架构的核心环节,需要兼顾:

| 设计维度 | 说明 |

|---|---|

| 信号完整性(SI) | 确保信号在传输过程中不失真 |

| 电源完整性(PI) | 保证电源供应稳定,减少噪声 |

| 时序收敛 | 满足信号的建立时间和保持时间要求 |

| 成本控制 | 在性能和成本之间取得平衡 |

注意:成熟的DRAM模板经过充分验证,不可轻易修改,否则可能引入信号完整性问题。

理解了链路设计后,我们深入了解DRAM颗粒的内部结构,这是数据实际存储的地方。

DRAM颗粒

DRAM颗粒是数据的实际存储载体,理解其内部结构对于掌握内存容量计算和性能优化至关重要。

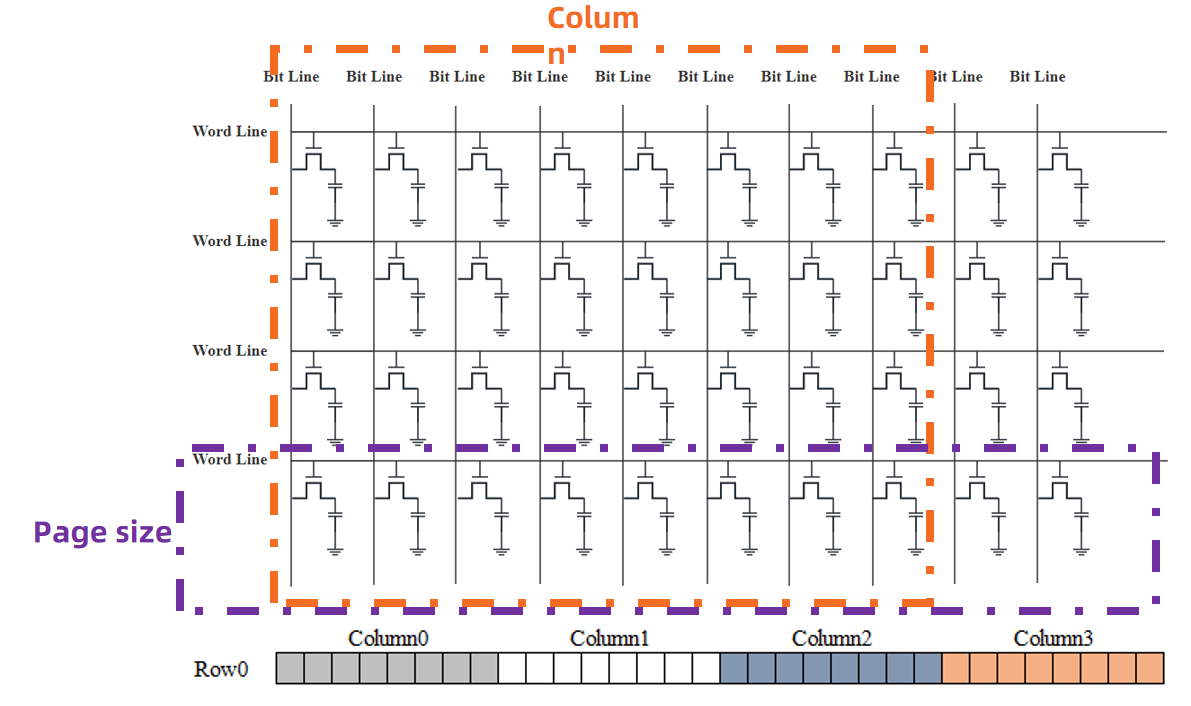

基本存储单元:Row、Column与Page Size

Row(行):等同于Word Line,将多个存储单元晶体管的gate端挂在一条线上,这条线称为row。激活某一行时,该行上所有存储单元的晶体管被打开。

Column(列):由Bit Line组成,一列包含多个Bit Line,具体数量取决于位宽。读取数据时,通过检测位线上的电压变化来判断存储的是0还是1。

Page Size:一行的大小称为Page Size,是内存访问的基本单位。

计算公式:

其中,列数由 Column Address 的位数决定:

因此:

Bank:独立的内存阵列

什么是Bank?

Bank是一个个独立的内存阵列,每个Bank包含自己的行解码器、列解码器和读放大器。

为什么需要多个Bank?

| 优势 | 说明 |

|---|---|

| 提高并行访问效率 | 不同Bank可以同时进行操作 |

| 减少等待时间 | 一个Bank在预充电时,可以访问另一个Bank |

| 提升有效带宽 | 多Bank交错访问,减少延迟影响 |

Bank的使用限制:

同一Bank内不能同时激活(Active)两个Row,而 Row 的激活和关闭(预充电Precharge)需要耗时。因此,多Bank设计可以减少存储单元预充电等待时间,提高整体访问效率。

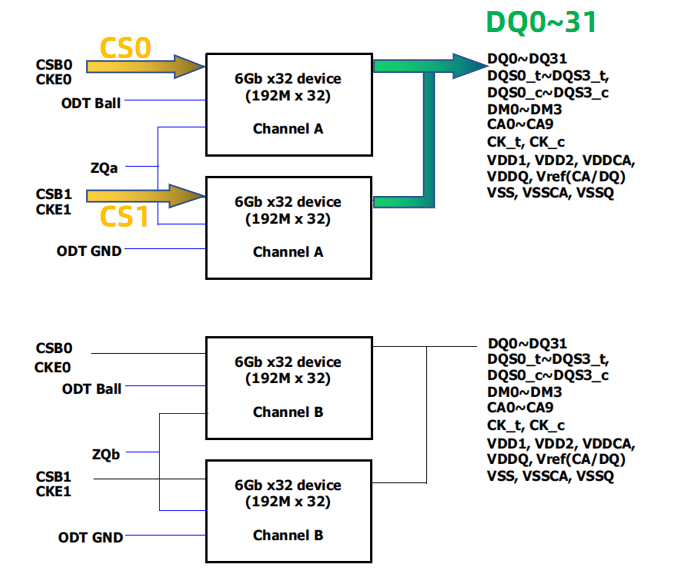

Rank:多颗粒协同工作

什么是Rank?

Rank是DRAM模块内部的逻辑结构,同一个Rank内的多个DRAM颗粒通过共享同一组控制信号协同工作,通过CS_n(片选)信号选择不同的Rank。

Rank的作用:

- 增加容量:多个Rank可以在同一Channel内共享DQ数据线,增加总内存容量

- 提高性能:不同Rank可以交错访问,隐藏预充电延迟

Rank与Channel的关系:

一个Channel内可以有多个Rank,这些Rank共用同一组DQ线,但通过片选信号独立控制。

位宽与Channel

SoC的位宽:决定了SoC一次能处理的数据宽度。

颗粒的位宽:

| DRAM类型 | 单颗粒位宽选项 | 常用位宽 | 说明 |

|---|---|---|---|

| DDR3/DDR4 | 4bit、8bit、16bit | 16bit | 多颗粒组合实现32bit位宽 |

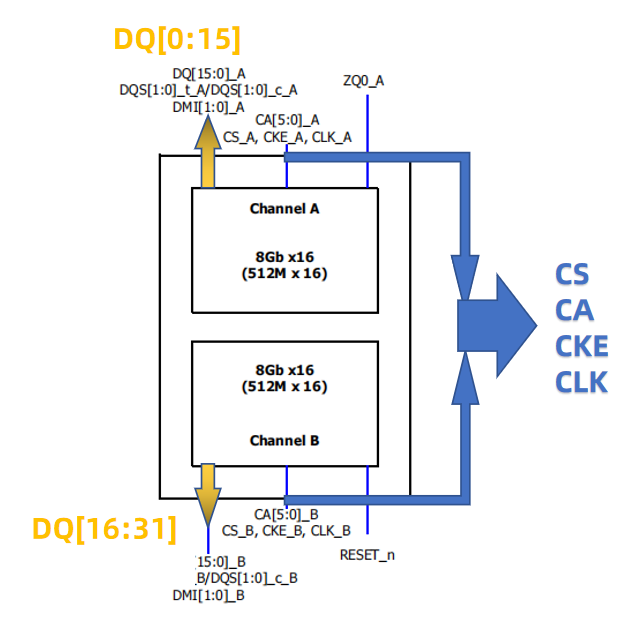

| LPDDR4 | 32bit | 32bit | 内部2个独立Channel,每个Die 16bit |

Channel(通道):

Channel是物理通道,每个Channel拥有独立的数据线、地址线和控制信号(时钟、片选等)。

Channel的优势:

- 多个Channel可并行传输数据

- 对带宽有显著提升效果

- 独立控制,互不干扰

掌握颗粒结构后,我们来看看DRAM的信号和Pin定义,理解数据是如何在颗粒和控制器之间传输的。

DRAM信号Pin

DRAM通过一组标准的信号Pin与外界通信,了解这些信号有助于理解DRAM的工作过程和调试问题。

信号分类

DRAM信号主要分为四类:

| 信号类型 | 主要信号 | 作用 |

|---|---|---|

| 时钟信号 | CK_t、CK_c | 提供采样时钟基准 |

| 命令/地址信号 | CA、CKE、CS#等 | 发送控制命令和寻址 |

| 数据信号 | DQ、DQS、DM | 传输读写数据 |

| 电源信号 | VDD、VDDQ等 | 为各部分供电 |

CK信号(时钟信号)

组成:包含CK_t和CK_c,是一对差分信号。

作用:作为CA信号的采样时钟,所有命令和地址信号都以CK为基准进行采样。

CA信号(命令/地址信号)

包含的信号:

命令信号:CKE、RST_N、CS#、ODT、RAS、CAS、WE、ACT等

地址信号:A0-A17(行/列地址)、BG0-BG1(Bank Group)、BA0-BA2(Bank地址)

作用:用于发送DRAM的相关控制命令和寻址,依据JEDEC协议规定。

数据信号

信号组成:

- DQS:数据选通信号,用于数据同步

- DQ:数据信号,传输实际的读写数据

- DM:数据掩码信号,用于写入时屏蔽部分字节

读写区分:

- wDQS/wDQ:写操作时的数据选通和数据信号

- rDQS/rDQ:读操作时的数据选通和数据信号

电源信号

| 电源名称 | 作用 | 说明 |

|---|---|---|

| VCC18-DRAM | 内部PHY供电 | 控制器端 |

| VDD-DRAM | 数字电路供电 | 一般与VDD-SYS合并 |

| VCC-DRAM/VCC-DRAML | IO供电 | 对应颗粒端VDDQ |

| VDD18-LPDDR | 颗粒端VDD1供电 | LPDDR专用 |

| VPP25-DRAM | 行激活电压 | DDR4专有 |

了解了信号定义后,我们再回到实际应用,看看如何从Datasheet获取颗粒信息并进行容量和带宽计算。

颗粒信息获取

在实际应用中,DRAM适配前需要从Datasheet中读取关键参数进行配置。

关键参数

从Datasheet中需要获取以下关键信息:

| 参数 | 说明 | 获取方式 |

|---|---|---|

| Part Number | 准确型号 | 通过丝印或原厂获取 |

| Configuration | 容量及内存结构 | Datasheet规格表 |

| Package | 封装类型 | Datasheet封装章节 |

| Frequency | 最高速率 | IO数据率,为工作频率的2倍 |

| DC Operating Conditions | 工作电压 | 电压范围要求 |

| Temperature Range | 工作温度 | 区分商业级/工业级 |

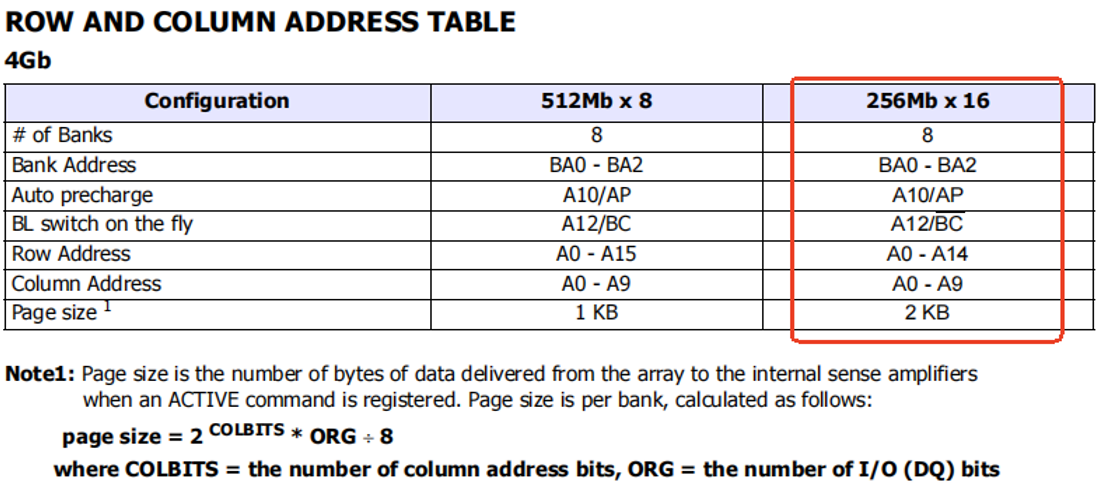

DRAM容量计算

示例:以某DDR3颗粒为例,从Datasheet获取以下信息:

Datasheet参数:

- 位宽:x16

- Bank Address:BA0-BA2(3位,8个Bank)

- Row Address:A0-A14(15位)

- Column Address:A0-A9(10位)

计算步骤:

- 计算行数: 行

- 计算列数: 列

- 计算Bank数: 个Bank

- 计算Page Size:

总容量计算:

DRAM带宽计算

DDR3/LPDDR3/DDR4带宽公式:

示例:DDR3 16bit,933MHz时钟

LPDDR4/4X带宽公式:

示例:LPDDR4 16×2bit,1600MHz时钟

实际带宽利用率

由于刷新、预充电等操作的开销,实际有效带宽低于理论带宽:

| DRAM类型 | DDR3 | LPDDR3 | DDR4 | LPDDR4 |

|---|---|---|---|---|

| 带宽利用率 | 60%-70% | 50%-60% | 60%-70% | 50%-60% |

通过掌握上述基础知识,可以更好地进行DRAM选型、系统设计和故障排查。