DRAM 参数调试

在掌握了DRAM基础知识后,本文介绍如何通过参数调试确保DDR子系统稳定运行。DDR调试涉及读写训练和信号完整性两个核心环节,直接影响系统的性能和稳定性。

本文适用读者:硬件工程师、驱动开发人员

DRAM 调试概述

为什么需要 DRAM 调试?

DRAM 子系统工作在高频环境下,信号传输受到多种因素影响:

| 影响因素 | 说明 |

|---|---|

| 信号完整性 | 高频信号在传输过程中会出现反射、衰减等问题,影响接收端采样 |

| 时序裕量 | 频率提升后,信号的建立时间和保持时间裕量减小,需要精确调整 |

| PVT变化 | 工艺、电压、温度的变化会影响信号延迟和驱动能力 |

| 颗粒差异 | 不同DRAM颗粒的特性存在差异,需要针对性配置 |

如果不进行调试,可能导致:

- 数据读写错误,系统不稳定

- 无法达到标称频率,性能受限

- 兼容性问题,部分颗粒无法正常工作

调试的主要内容

DDR调试主要包含两个方面:

读写训练(Training):帮助每个信号找到眼图上的最佳采样点,确保在各种条件下都能正确采样数据。

信号完整性优化:通过调整驱动能力和端接电阻,优化信号眼图质量,获得更大的时序和电压裕量。

理解调试目标后,我们先学习读写训练的核心原理。

读写训练原理

什么是读写训练?

读写训练(Training)是DDR初始化过程中的关键步骤,目的是为每个信号找到最佳的采样点。

核心思路:

- 在电压轴上寻找最佳参考电平(Vref)

- 在时间轴上寻找最佳采样时刻(延迟值)

- 两者结合确定眼图的中心位置

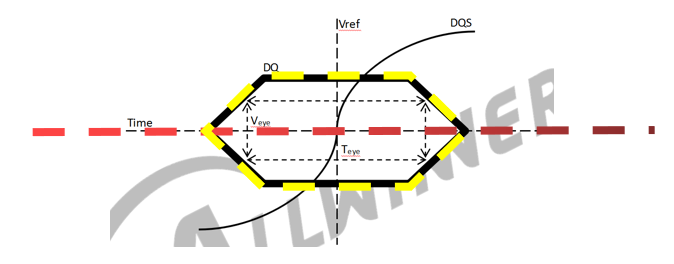

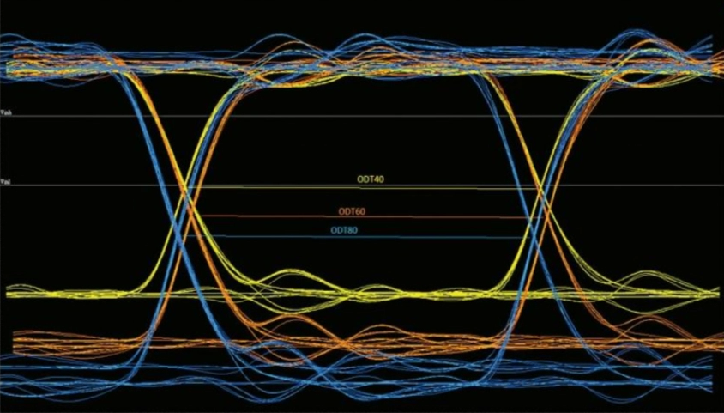

眼图与采样点

什么是眼图?

眼图是评估信号质量的可视化工具,通过叠加多次传输的信号波形形成。眼图的"眼睛"张开越大,表示信号质量越好,采样裕量越大。

最佳采样点的确定:

| 轴方向 | 寻找目标 | 方法 |

|---|---|---|

| 电压轴 | 最佳Vref值 | 找时间裕量最大的电压值 |

| 时间轴 | 最佳延迟值 | 在最佳Vref上找左右边界,取中心 |

信号相位关系

不同类型的信号之间存在特定的相位关系,正确理解这些关系是调试的基础。

CK与CA/CS相位

CK(时钟)信号用于采样CA(命令/地址)和CS(片选)信号。

初始相位要求:

- CK的相位比CA/CS大90度

- 这样可以满足在CK上升沿采样时,CA/CS信号已稳定

WDQS与WDQ相位(写方向)

WDQS(写数据选通)和WDQ(写数据)从PHY端发出时基本对齐,但需要调整相位关系以满足颗粒端采样要求。

不同DRAM类型的相位要求:

| DRAM类型 | 相位关系 | 说明 |

|---|---|---|

| DDR3/DDR4/LPDDR3 | WDQS比WDQ大90度 | 颗粒在DQS边沿采样DQ |

| LPDDR4/4X | WDQ比WDQS大90度 | 颗粒在DQ中心采样 |

RDQS与RDQ相位(读方向)

RDQS(读数据选通)和RDQ(读数据)由颗粒端发出。

相位关系:

- 颗粒发出的RDQS和RDQ是边沿对齐的

- 主控端需要将RDQS的相位设置得比RDQ大90度

- 这样主控可以在DQS边沿正确采样DQ数据

眼宽范围调试

在保证DRAM能正常读写的前提下,通过调节DQ信号及DQS采样信号,可以得出每个信号的可用范围。将延迟值设置到可用范围的中心点,即为当前最优配置。

调试方法:

- 固定DQS延时值为0,调节DQ延时值,记录能正常读写的DQ延时范围

- 如果DQ延时值为0也能正常读写,固定DQ延时值为0,调节DQS延时值,记录能正常读写的DQS延时范围

- 计算中心点:DQS延时最大值到DQ延时最大值这段范围内的中心值

完成读写训练后,还需要优化信号完整性以保证眼图质量。

信号完整性优化

什么是信号完整性?

信号完整性(Signal Integrity, SI)是指信号在传输过程中保持其原始特征的能力。在高频环境下,信号会受到反射、衰减、串扰等影响,导致接收端信号失真。

信号完整性调试的目标:

- 阻抗匹配:减少信号反射

- 眼图优化:增大眼高和眼宽

- 时序裕量:满足建立/保持时间要求

- 电源稳定:抑制噪声和纹波

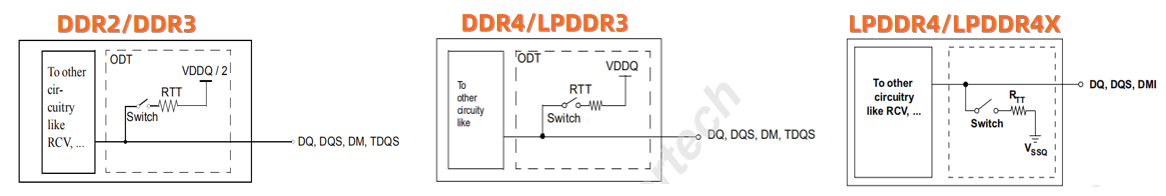

端接模型

什么是端接(ODT)?

端接(On-Die Termination, ODT)是在芯片内部添加电阻,用于匹配传输线阻抗,消除信号反射。没有端接时,信号在阻抗不匹配点会产生反射,影响信号质量。

输出驱动模型:

输出驱动采用推挽结构:

- 输出高电平:上拉电阻导通,下拉电阻截止

- 输出低电平:下拉电阻导通,上拉电阻截止

端接电阻位置:

不同DRAM类型的端接配置不同:

| DRAM类型 | 端接信号 | 说明 |

|---|---|---|

| DDR3/DDR4/LPDDR3 | DQS、DQ、DM | 仅数据信号有端接 |

| LPDDR4/4X | DQS、DQ、DM、CK、CA | 数据和命令信号都有端接(除RESET和CKE) |

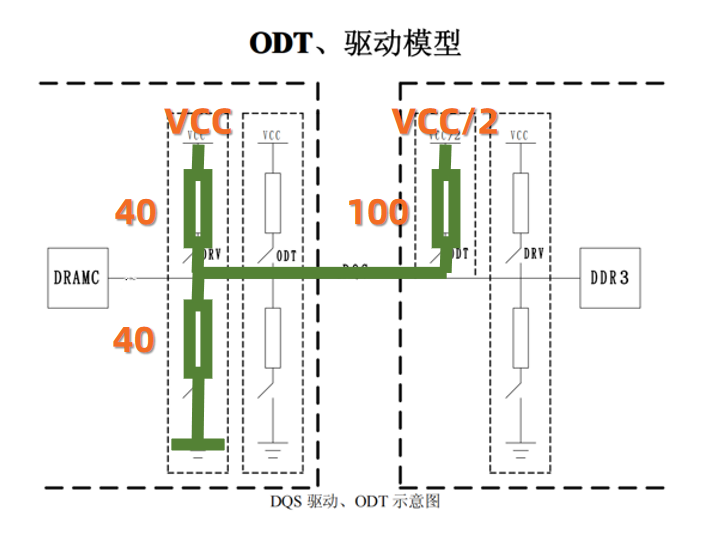

驱动能力与ODT配置

驱动能力(DRV)和端接电阻(ODT)的默认配置按SI仿真建议进行,后续根据实际调试情况确定最优值。

配置原则:

- 驱动电阻越小,驱动能力越强,信号边沿越陡

- 端接电阻需要与传输线阻抗匹配,减少反射

Vref 理论计算

什么是Vref?

Vref 是接收端的参考电平,用于判断接收信号是高电平还是低电平。最佳 Vref 应该设置在眼图中心。

DDR3示例计算

以DDR3为例,假设:

- DQ驱动能力设置为

- ODT电阻设置为

- 工作电压

高电平计算:

输出高电平时,上拉导通,分压电路为:

代入参数:

低电平计算:

输出低电平时,下拉导通,分压电路为:

代入参数:

最佳Vref:

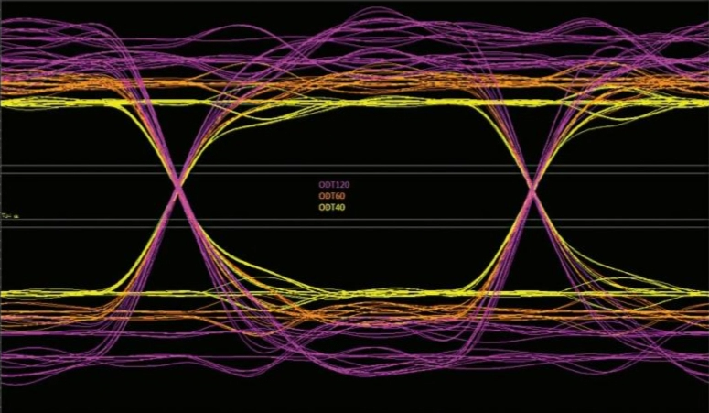

DDR4/LPDDR4差异

不同DRAM类型的最佳Vref位置存在差异:

DDR3:

- 接收端ODT从 减弱到 时,信号幅度变大

- 最优Vref始终固定在

| 颜色 | ODT值 |

|---|---|

| 紫色 | |

| 橙色 | |

| 黄色 |

DDR4:

- 接收端ODT从 增强到 时,信号幅度变小

- 低电平被拉高,高电平基本固定在

- 最优Vref随ODT强度增加而上移()

| 颜色 | ODT值 |

|---|---|

| 蓝色 | |

| 绿色 | |

| 黄色 |

各DRAM类型最佳Vref汇总

| DRAM类型 | CA颗粒接收Vref | DQ读方向主控Vref | DQ写方向颗粒Vref |

|---|---|---|---|

| DDR3 | 引脚输入, | 寄存器设置, | 引脚输入, |

| DDR4 | 引脚输入, | 寄存器设置, | MR调节, |

| LPDDR3 | 引脚输入, | 寄存器设置, | 引脚输入, |

| LPDDR4/4X | MR调节, | 寄存器设置, | MR调节, |

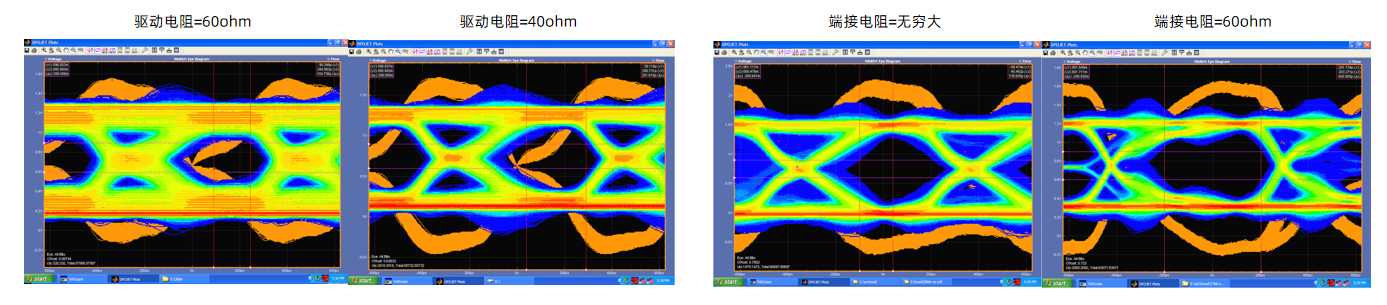

眼图调优实践

提频过程中,如果眼图眼宽或眼高变小,可以通过驱动电阻和端接电阻进行调节。

驱动电阻调节效果:

驱动电阻阻值越小,驱动能力越强:

- 信号边沿越陡

- 眼图眼高越大

- 但可能引入更多噪声

端接电阻调节效果:

端接电阻阻值越小,导流能力越强:

- 信号边沿越缓

- 眼图眼高越小

- 但能更好地吸收反射

理解调试原理后,本节介绍具体的配置参数。

DRAM配置参数详解

参数概述

DRAM参数保存在 sys_config.fex 配置文件中,用于初始化DDR子系统。参数主要分为以下几类:

| 参数类别 | 主要参数 | 作用 |

|---|---|---|

| 时钟与类型 | dram_clk, dram_type | 设置工作频率和DRAM类型 |

| 容量配置 | dram_para1, dram_para2 | 配置Bank、Row、Col、位宽等 |

| 驱动与端接 | dram_zq, dram_odt_en | 配置驱动能力和端接电阻 |

| 相位延迟 | dram_tpr10/11/12 | 调整信号相位延迟 |

| 模式寄存器 | dram_mr0~mr3 | 配置DRAM工作模式 |

典型配置示例:

[dram_para]

dram_clk = 1056

dram_type = 3

dram_zq = 0x7b6bfb

dram_odt_en = 0x1

dram_para1 = 0x000010d2

dram_para2 = 0x00000000

dram_mr0 = 0x1c70

dram_mr1 = 0x2

dram_mr2 = 0x18

dram_mr3 = 0x0

dram_tpr0 = 0x004A2195

dram_tpr1 = 0x02423190

dram_tpr2 = 0x0008B061

dram_tpr3 = 0xB4787896

dram_tpr4 = 0x0

dram_tpr5 = 0x48484848

dram_tpr6 = 0x48

dram_tpr7 = 0x1621121e

dram_tpr8 = 0x0

dram_tpr9 = 0x0

dram_tpr10 = 0x0

dram_tpr11 = 0x00460000

dram_tpr12 = 0x00000055

dram_tpr13 = 0x34010100

参数配置器

配置导入

粘贴已有的 dram_para 配置文本,点击解析后会自动填充到下方各参数输入框。

基础配置(容量参数)

自动计算结果

Page Size: 0 Bytes (0 B)

DRAM 总容量: 0.00 MB

基础参数输出

dram_clk: 1056

dram_type: 3 (DDR3)

dram_para1: 0x0

dram_para2: 0x0

高级配置(驱动/ODT/相位/MR)

驱动能力与ODT配置

相位延迟配置 (范围: 0-F)

MR 寄存器配置 (十六进制, 参考对应JEDEC协议文档)

高级参数输出

dram_zq: 0x0

dram_odt_en: 0x1

dram_tpr10: 0x0

dram_tpr11: 0x0

dram_tpr12: 0x0

dram_mr0: 0x1c70

dram_mr1: 0x2

dram_mr2: 0x18

dram_mr3: 0x0

参数配置

[dram_para] dram_clk = 1056 dram_type = 3 dram_zq = 0x0 dram_odt_en = 0x1 dram_para1 = 0x0 dram_para2 = 0x0 dram_mr0 = 0x1c70 dram_mr1 = 0x2 dram_mr2 = 0x18 dram_mr3 = 0x0 dram_tpr0 = 0x004A2195 dram_tpr1 = 0x02423190 dram_tpr2 = 0x0008B061 dram_tpr3 = 0xB4787896 dram_tpr4 = 0x0 dram_tpr5 = 0x48484848 dram_tpr6 = 0x48 dram_tpr7 = 0x1621121e dram_tpr8 = 0x0 dram_tpr9 = 0x0 dram_tpr10 = 0x0 dram_tpr11 = 0x0 dram_tpr12 = 0x0 dram_tpr13 = 0x34040500

时钟与类型参数

dram_clk

DRAM时钟信号频率,单位为MHz。

说明:

- 例如 672 表示时钟频率为 672MHz

- 数据速率 = (DDR双倍速率)

- 例如 672MHz 时钟对应 Mbps 数据速率

- 调整最小步进单位为 12MHz

dram_type

DRAM类型配置。

| 值 | DRAM类型 |

|---|---|

| 2 | DDR2 |

| 3 | DDR3 |

| 4 | DDR4 |

| 6 | LPDDR2 |

| 7 | LPDDR3 |

| 8 | LPDDR4 |

| 9 | LPDDR5 |

容量配置参数

dram_para1

配置Bank数量、地址行数、页大小。

| BIT | 含义 |

|---|---|

| 31:16 | RFU(预留,不要使用) |

| 15:12 | Bank Size:Bank数量 0 = 4 banks 1 = 8 banks |

| 11:4 | Row Number:地址行数 |

| 3:0 | Page Size:页大小 0 = 512Byte 1 = 1KByte 2 = 2KByte 4 = 4KByte 8 = 8KByte |

dram_para2

配置DRAM容量、Rank数量、总线位宽。

| BIT | 含义 |

|---|---|

| 31 | Size Mode: 0 = 自动识别DRAM大小 1 = 使用手动提供的DRAM大小 |

| 30:16 | DRAM Size(需配置Bit 31启用): n = n MByte |

| 15:12 | Rank Number: 0 = 1 Rank 1 = 2 Rank |

| 11:4 | RFU(预留,不要使用) |

| 3:0 | Bus Width: 0 = 16bit(Full DQ) 1 = 8bit(Half DQ) |

dram_para1 和 dram_para2 用于容量识别结果回写,或手动强制配置容量。一般使用自动识别,无需手动配置。

驱动与端接参数

dram_odt_en

控制器DX读ODT使能。

| BIT | 含义 |

|---|---|

| 31:1 | RFU(预留,不要使用) |

| 1:0 | Read ODT: 0 = 关闭 1 = 开启 |

dram_zq

控制器DX ODT、输出驱动能力,以及CK、CA输出驱动能力配置。

| BIT | 含义 |

|---|---|

| 23:20 | DX2/3 ODT(不使用): 0x1 = 0x2 = 0x3 = 0x4 = 0x5 = 0x6 = 0x7 = |

| 19:16 | DX2/3 驱动能力(不使用): 0x0 = 0x1 = 0x3 = 0x5 = 0x7 = 0xb = 0xf = |

| 15:12 | DX0/1 ODT: 0x1 = 0x2 = 0x3 = 0x4 = 0x5 = 0x6 = 0x7 = |

| 11:8 | DX0/1 驱动能力: 0x0 = 0x1 = 0x3 = 0x5 = 0x7 = 0xb = 0xf = |

| 7:4 | CK 驱动能力: 0x1 = 0x2 = 0x3 = 0x4 = 0x5 = 0x6 = 0x7 = |

| 3:0 | CA 驱动能力: 0x0 = 0x1 = 0x3 = 0x5 = 0x7 = 0xb = 0xf = |

驱动和 ODT 阻值档位因芯片而异。档位越高,阻值越小,驱动或端接能力越强。

V86x 芯片是 16 位 DDR,所以 DX2/DX3 不使用,配置不生效

相位延迟参数

dram_tpr10

调整CK、CA、CS信号的相位延迟。

| BIT | 含义 |

|---|---|

| 31:16 | RFU(预留,不要使用) |

| 15:12 | CS1 Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF 只对2个CS的DDR3/DDR4有效 |

| 11:8 | CS0 Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 7:4 | CA Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 3:0 | CK Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

dram_tpr11

调整DQS/DQ写方向的相位延迟。

| BIT | 含义 |

|---|---|

| 31:24 | RFU(预留,不要使用) |

| 23:20 | DQS1 Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 19:16 | DQS0 Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 7:4 | DX1 Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 3:0 | DX0 Write bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

dram_tpr12

调整DQS/DQ读方向的相位延迟。

| BIT | 含义 |

|---|---|

| 31:24 | RFU(预留,不要使用) |

| 23:20 | DQS1 Read bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 19:16 | DQS0 Read bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 7:4 | DX1 Read bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

| 3:0 | DX0 Read bit delay: [0:3] delay值,范围 0x0 ~ 0xF |

其他参数

dram_tpr5

配置主控端CA VREF、DX读数据内部VREF。与控制器相关,一般不建议修改。

dram_tpr13

灵活用于功能控制等用途,具体因项目而异,没有固定规范。

dram_mr0~mr3

对应JEDEC规范的MR寄存器:

| 参数 | 说明 |

|---|---|

| dram_mr0 | MR0寄存器,对应JEDEC DDR3/DDR4/LPDDR3/LPDDR4规范 |

| dram_mr1 | MR1寄存器,对应JEDEC规范 |

| dram_mr2 | MR2寄存器,对应JEDEC规范 |

| dram_mr3 | MR3寄存器,对应JEDEC规范 |

具体寄存器位定义请参考相应DRAM类型的JEDEC规范文档。

调试流程建议

掌握上述知识后,DDR调试可按以下流程进行:

-

初始化配置

- 根据颗粒Datasheet设置dram_type、dram_clk

- 使用默认驱动能力和ODT配置

-

读写训练

- 执行Read/Write Training确定最佳延迟值

-

信号完整性优化

- 检查眼图质量

- 根据眼高/眼宽情况调整驱动和端接电阻

- 调整Vref到最佳位置

-

稳定性验证

- 进行压力测试(长时间读写、温度变化)

- 验证不同颗粒的兼容性

通过合理的参数调试,可以确保DDR子系统在各种工作条件下稳定运行,发挥最佳性能。